Simulink Design Verifier utilise des méthodes formelles pour identifier les erreurs de design cachées dans les modèles. Il détecte les blocs du modèle qui entraînent des problèmes de dépassement d'entier, de logique morte, de violation d'accès aux tableaux et de division par zéro. Il peut vérifier de manière formelle que le design répond aux exigences fonctionnelles. Pour chaque erreur de design et chaque exigence non respectée, il génère un cas de test de simulation pour le débuggage.

Simulink Design Verifier génère des cas de test pour la couverture du modèle ainsi que des objectifs personnalisés afin d'étendre les cas de tests existants basés sur les exigences. Ces cas de test permettent à votre modèle de remplir les objectifs de condition, de décision, de condition/décision modifiée (MCDC) et les objectifs de couverture personnalisés. En plus des objectifs de couverture, vous pouvez spécifier des objectifs de test personnalisés pour générer automatiquement des cas de test basés sur les exigences.

Le support des normes industrielles est assuré par l'IEC Certification Kit (for ISO 26262 and IEC 61508) et le DO Qualification Kit (for DO-178 and DO-254)

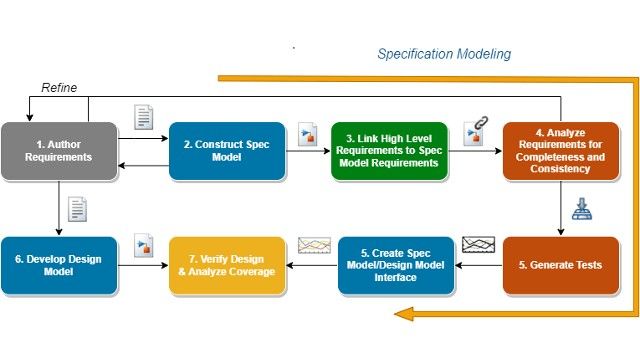

Valider les exigences

Vérifiez les exigences modélisées pour assurer leur cohérence et leur exhaustivité avant de commencer votre design.

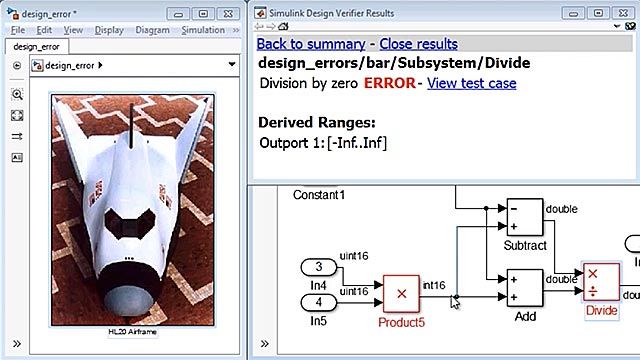

Détecter les erreurs run-time et de diagnostic

Avant même d'exécuter des simulations, vous pouvez détecter les erreurs de modélisation et run-time, notamment le dépassement d'entier, la division par zéro, l'indexation de tableaux hors limites, les valeurs dénormalisées et les erreurs de virgule flottante, ainsi que les erreurs de validité des données.

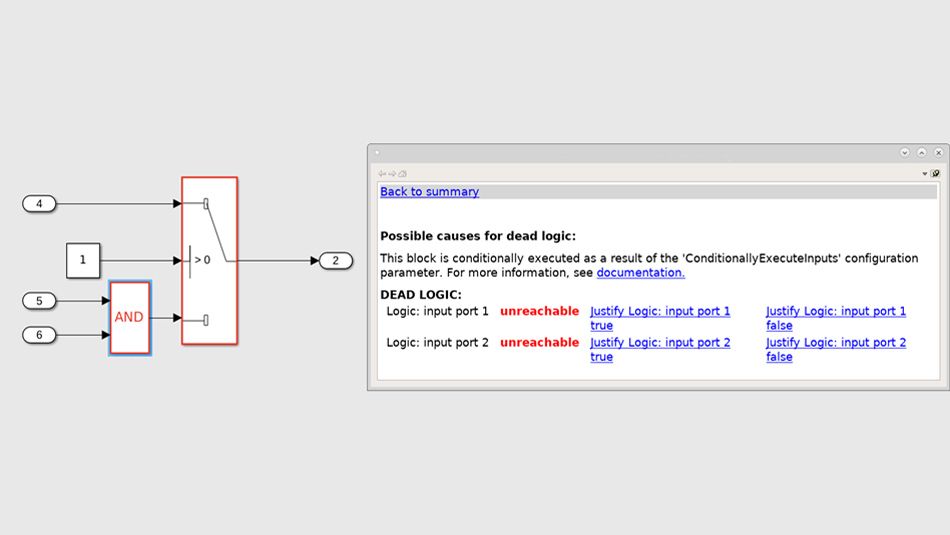

Trouver la logique morte

Trouvez dans votre modèle les objets qui ne peuvent pas être activés pendant la simulation et l'exécution du code généré.

Analyser la couverture de test manquante

Améliorez et étendez les cas de test existants créés manuellement pour résoudre les problèmes de couverture manquante dans les modèles, le code généré et le code C/C++ appelé depuis les blocs Simulink et dans les diagrammes Stateflow.

Vérifier les exigences formelles de sécurité

Vérifiez que votre design se comporte conformément aux exigences de sécurité (3:53) définies formellement avec MATLAB, Simulink et Stateflow.

Créer des cas de test basés sur les exigences

Générez des cas de test à partir de modèles d'exigences système.

Ressources produits :

« En nous permettant d'analyser rapidement les exigences, de réutiliser les designs de produits précédents et d'éliminer les erreurs de codage manuel, l'approche Model-Based Design a réduit nos temps de développement. Ainsi, nous pouvons désormais répondre plus rapidement aux demandes de nos clients. »

MyoungSuk Ko, LS Automotive