Build and Run Executable on AMD SoC Devices

Configure a Simulink® model to generate code, build an executable, and then run the executable on your AMD® SoC device. The executable runs in the Linux® environment on the ARM® Cortex®-A processor on the AMD SoC device.

Configure the Model

This section shows you how to configure a new model or existing model to

Create a new model in Simulink. In Simulink, on the Simulation tab, select New > Blank Model. You can also open and use an existing model.

On the Apps tab, click the arrow on the far right of the Apps section. In the Setup to Run on Hardware gallery, click Run on Hardware Board.

On the Run on Hardware Board dialog box, set Hardware Board to

AMD Zynq ZC702 evaluation kitor one of the other supported Zynq® boards. Click Finish.(Optional) You can inspect the settings added to model from choosing the

AMD Zynq ZC702 evaluation kitas the Hardware board. On the Hardware tab, click Hardware Settings to open the model Configuration Parameters window.Save the changes to the model.

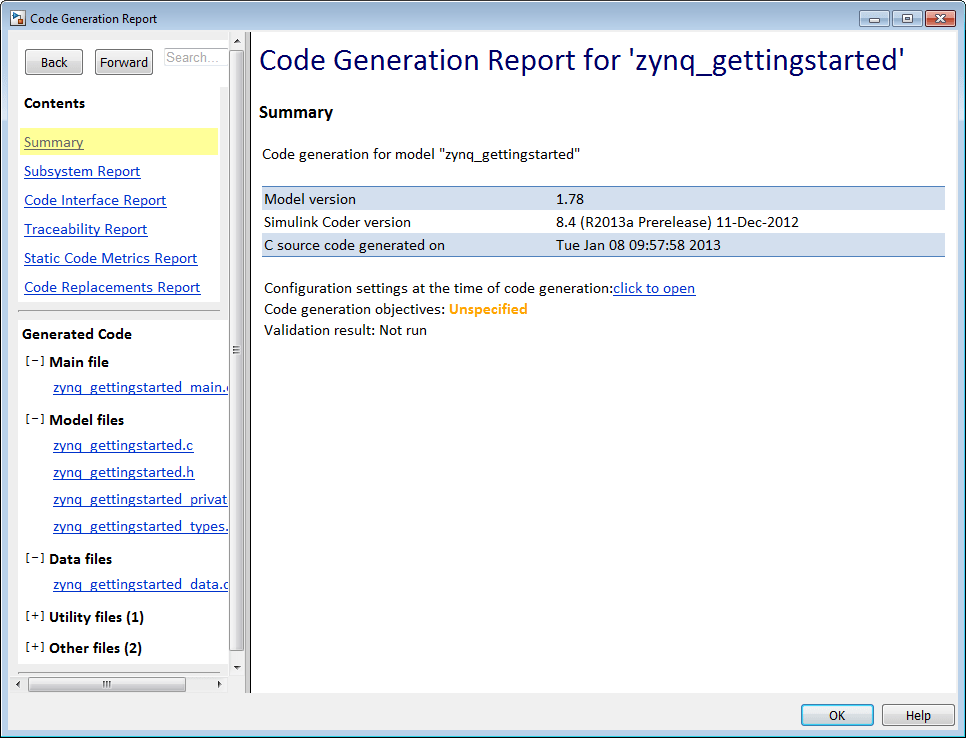

Build, Deploy, and Start the Model as an Executable

This section shows you how to build, deploy, and run your model as an executable binary on the ARM Cortex-A processor of the AMD SoC device.

Note

If your host computer is connected to multiple Zynq boards, disconnect the ones not being using.

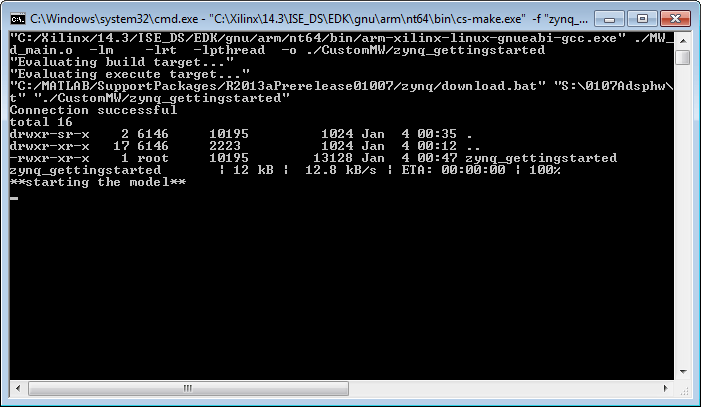

On the Hardware tab, click Deploy > Build, Deploy & Start.

When the build completes, the executable gets deployed to the hardware board and starts running. A command-line status window opens.

By default, the executable runs on a single core. PIL simulation and PIL-based execution profiling require single-core execution. To configure the executable to run on both cores, see Multicore Processor Targets.

Note

If a connection timeout error occurs during the download of the executable, see Troubleshooting AMD SoC Device and Development Computer Connection.

See Also

Hardware Implementation Pane: AMD Zynq ZC702/ZC706 Evaluation Kits | Hardware Implementation Pane: ZedBoard