Using Xilinx System Generator for DSP with HDL Coder

This example shows how to use Xilinx® System Generator for DSP with HDL Coder™.

Introduction

Using the Xilinx System Generator Subsystem block enables you to model designs using blocks from both Simulink® and Xilinx, and to automatically generate integrated HDL code. HDL Coder™ generates HDL code from the Simulink blocks, and uses Xilinx System Generator to generate HDL code from the Xilinx System Generator Subsystem blocks.

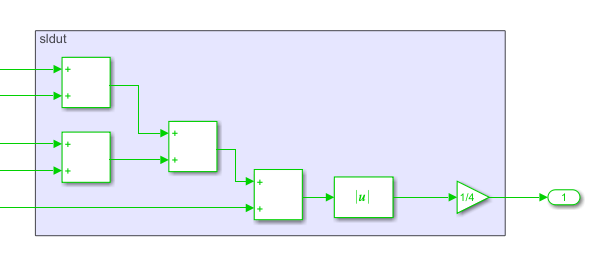

In this example, the design, or code generation subsystem, contains two parts: one with Simulink native blocks, and one with Xilinx blocks. The Xilinx blocks are grouped into a Xilinx System Generator Subsystem sysgendut that is inside a SLandSysGen Subsystem at the top level of the model hdlcoder_slsysgen. System Generator optimizes these blocks for Xilinx FPGAs. In the rest of the design, Simulink blocks and HDL Coder offer model-based design capabilities and HDL optimizations, such as distributed pipelining and delay balancing.

open_system('hdlcoder_slsysgen'); open_system('hdlcoder_slsysgen/SLandSysGen');

Perform Model-Level Optimizations for Simulink® Components

In this example, a sum tree indicated by the sldut section inside the SLandSysGen Subsystem is modeled with Simulink blocks. You can use distributed pipelining feature to take care of the speed optimization.

Distributed pipelining can move pipeline registers into the sum tree to reduce the critical path without changing the model function. Other optimizations, such as resource sharing, are also available, but not used in this example.

open_system('hdlcoder_slsysgen/SLandSysGen');

Create Xilinx System Generator Subsystem

To create a Xilinx System Generator subsystem:

Put the Xilinx blocks in one subsystem and leave the HDL architecture set to default value of

Module.Place a System Generator token at the top level of the subsystem. You can have subsystem hierarchy in a Xilinx System Generator Subsystem, but there must be a System Generator token at the top level of the hierarchy.

open_system('hdlcoder_slsysgen/SLandSysGen/sysgendut');

Configure Gateway In and Gateway Out Blocks

In each Xilinx System Generator subsystem, you must connect input and output ports directly to Gateway In and Gateway Out blocks.

Gateway In blocks must not do non-trivial data type conversion. For example, a Gateway In block can convert between uint8 and UFix_8_0, but changing data sign, word length, or fraction length is not allowed.

Generate HDL Code

You can use either makehdl at the command line or HDL Workflow Advisor to generate HDL code. To use makehdl:

makehdl('hdlcoder_slsysgen/SLandSysGen');

You can also generate a testbench, simulate, and synthesize the design as you would for any other model.