HDMI Tx

Convert YCbCr 4:2:2 pixel stream to video frame

Libraries:

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU102

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZC706

SoC Blockset Support Package for AMD FPGA and SoC Devices /

Zynq-7000 /

ZedBoard

SoC Blockset Support Package for AMD FPGA and SoC Devices /

MPSoC /

ZCU106

Description

Add-On Required: This feature requires the SoC Blockset Support Package for AMD FPGA and SoC Devices add-on.

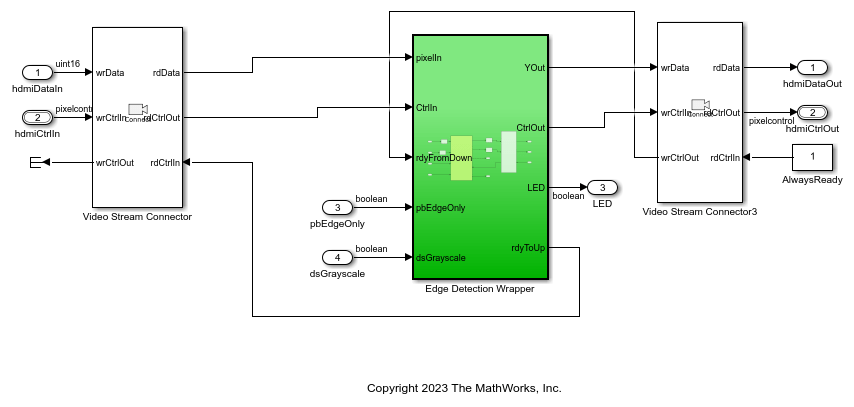

The HDMI Tx block converts a pixel stream in YCbCr 4:2:2 format to raw video data for display during simulation. It can return data in pixel stream mode for hardware algorithm design or in frame mode for faster simulation. When you include this block in your design, the SoC Builder tool generates all the IP blocks necessary to transmit video data to the FMC-HDMI-CAM card attached to your hardware board. None of the block parameters affect hardware behavior.

You must have Computer Vision Toolbox™ to use this block.

Examples

Limitations

In the hardware setup, select one of the supported Xilinx® boards. You can find the supported boards in the Libraries list at the top of this page. Set Add-on Card to

None.This block supports SoC generation using the SoC Builder tool. This block does not support the IP core generation workflow. For more information on workflows, see SoC Generation Workflows.

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2019a