F2837xD/F2838x/F2838x-M4 IPC Transmit

Transmit data to either core while using separate model for each core

Libraries:

C2000 Microcontroller Blockset /

F2837xD

C2000 Microcontroller Blockset /

F2838x /

C28x

C2000 Microcontroller Blockset /

F2838x /

M4

C2000 Microcontroller Blockset /

F28p65x

Description

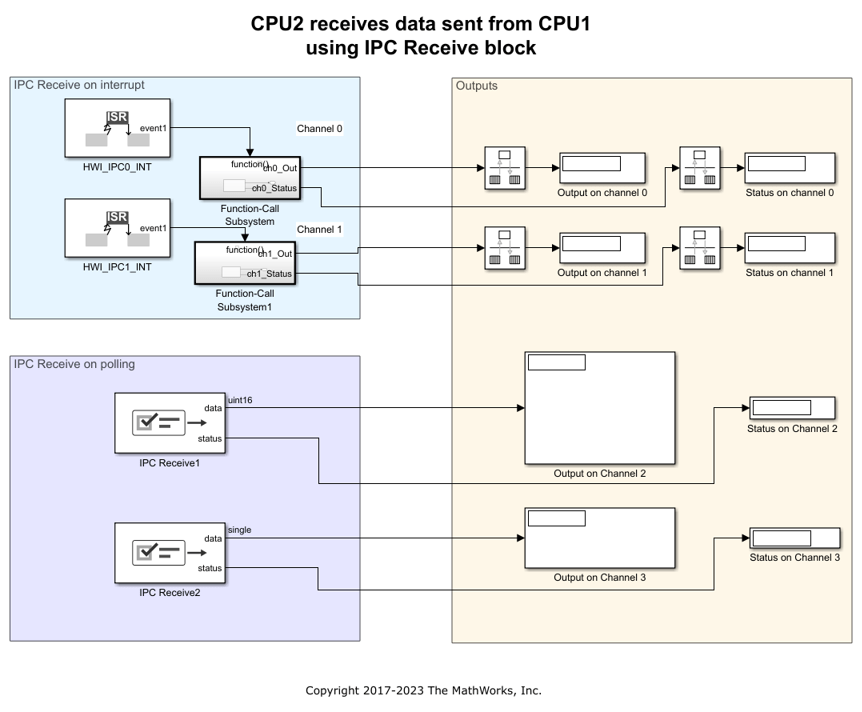

The IPC Transmit block transmits data from one Core to the other.

Note

Use IPC Receive and IPC Transmit blocks to receive or sent data to either core for multi-core processors. Use these blocks for flat model approach where you are using separate models for each core.

If you are using multiprocessor modeling approach with single model triggering multiple cores using Task Manager, use the Interprocess Data Read and Interprocess Data Write blocks to send and receive data between cores.

Core1 transmits data to its allocated memory (Core1-to-Core2 Message RAM) and receives data from the allocated memory of Core2 (Core2-to-Core1 Message RAM). Similarly Core2 transmits data to its allocated memory (Core2-to-Core1 Message RAM) and receives data from allocated memory of Core1 (Core1-to-Core2 Message RAM). For F2838xD, Core1/Core2 can be CPU1,CPU2 or ARM Cortex-M4 (CM) and for F2837xD, Core1/Core2 can be CPU1 or CPU2.

If Core1 and Core2 are both C28x core, then the data and channel structure between two cores are allocated in Message RAM and the data array is allocated in Global Shared RAM. In C28x core, by default all the channel structures are created in Message RAM.

However, if one of the core is ARM Cortex M4 (applicable only for F2838x), then the data array is allocated only using Message RAM as global shared RAM is not available between cores. In order to accommodate more data, only required channel structures are created in Message RAM. Hence if the channel number used for transmit block in one core does not match with the receive block in other core the data transmission will not occur.

For more information on how the memory is allocated for IPC block, see Memory Allocation for IPC Flat Models

Examples

Ports

Input

Parameters

Version History

Introduced in R2018a