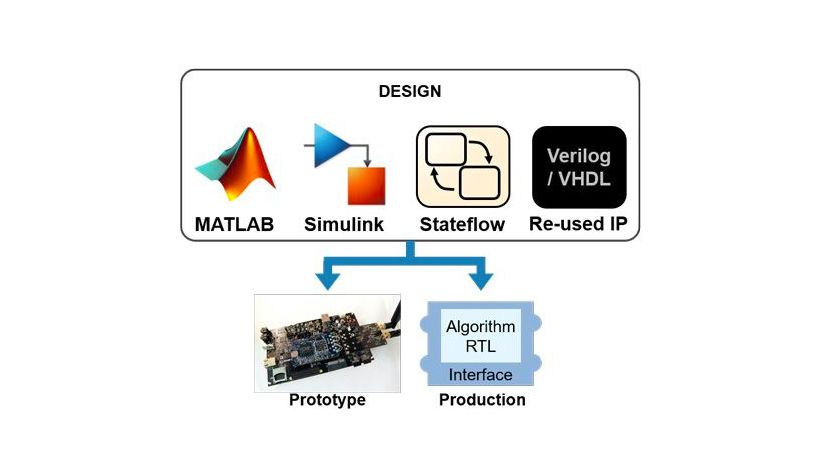

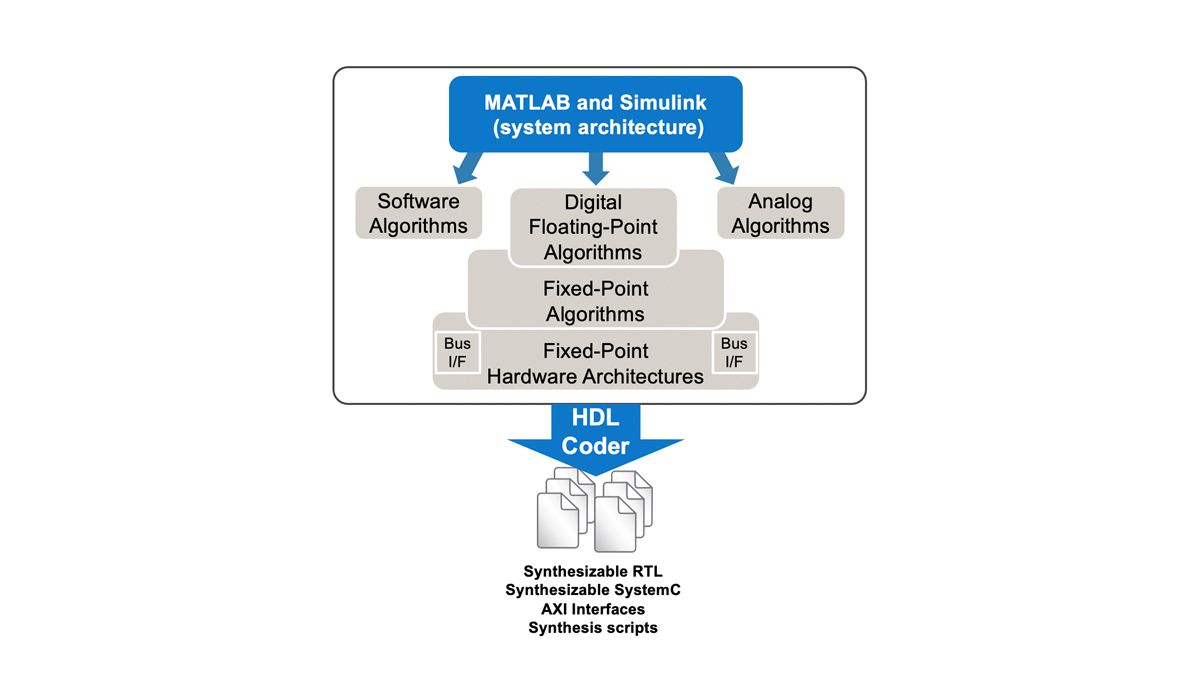

HDL Coder permet le design de haut niveau pour les FPGA, SoC et ASIC en générant du code Verilog® et VHDL® portable et synthétisable à partir de fonctions MATLAB, de modèles Simulink® et de diagrammes Stateflow. Vous pouvez utiliser le code HDL généré pour la programmation FPGA, le prototypage ASIC et le design de production.

HDL Coder comprend un outil de conseil pour ce workflow qui automatise le prototypage du code généré sur les cartes AMD®, Intel® et Microchip et génère des cœurs IP pour les workflows ASIC et FPGA. Vous pouvez optimiser la vitesse et la surface, mettre en évidence les chemins critiques et générer des estimations de l'utilisation des ressources avant la synthèse. HDL Coder assure la traçabilité entre les modèles Simulink et le code Verilog et VHDL généré, ce qui permet de vérifier le code pour les applications de haute intégrité respectant la norme DO-254 ainsi que d'autres normes.

Design hardware de haut niveau

Concevez votre sous-système en choisissant parmi plus de 300 blocs Simulink et fonctions MATLAB compatibles avec le HDL ; ajoutez des diagrammes Stateflow, des modèles Simscape et des réseaux de Deep Learning. Simulez le comportement hardware de votre design, explorez des architectures alternatives et générez du code VHDL ou Verilog synthétisable en utilisant des types de données à virgule fixe ou flottante, ou une combinaison des deux.

Ciblage indépendant du fournisseur

Générez du RTL synthétisable optimisé pour les FPGA des principaux fournisseurs et utilisez-le également pour les ASIC. Réutilisez les mêmes modèles pour la génération de code de prototypage et de production.

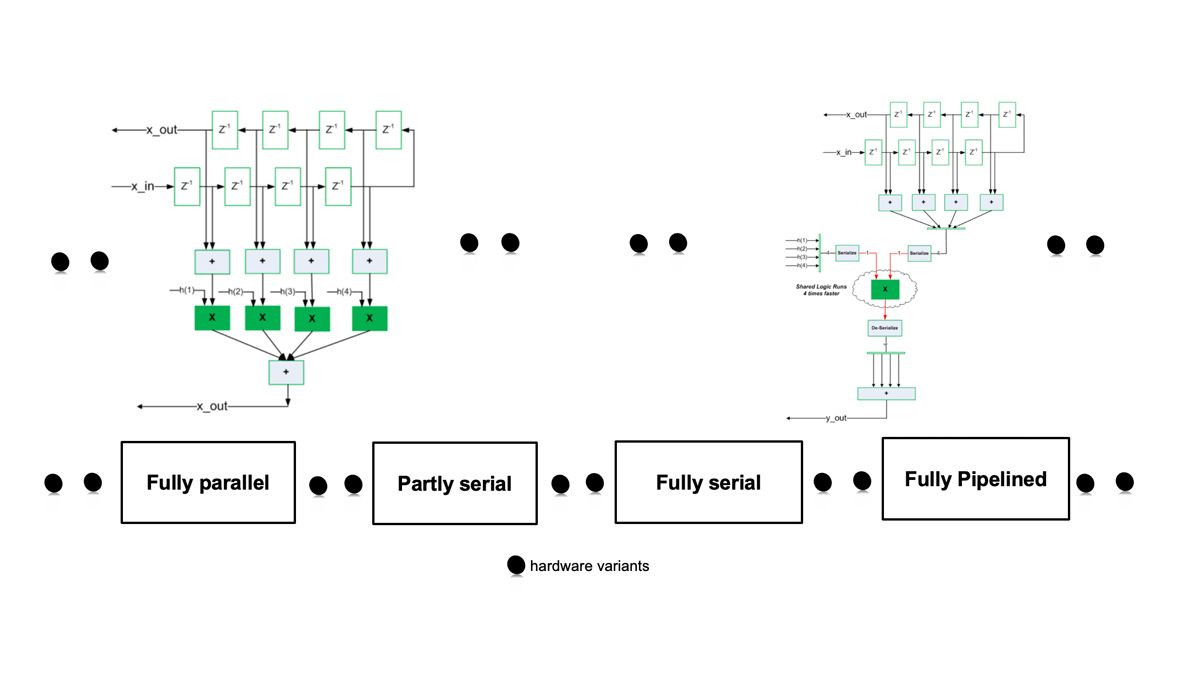

Optimisation du design

Explorez une grande variété d'architectures hardware et d'options de quantification en virgule fixe avant de vous engager dans une implémentation RTL. Utilisez des optimisations de synthèse de haut niveau telles que le partage des ressources, le pipelining et l'équilibrage des retards, qui se mappent efficacement sur les ressources de la cible telles que la logique, les DSP et les RAM.

Cartes basées sur des FPGA

Générez du code RTL qui se met en correspondance efficacement avec des cartes FPGA et SoC AMD, Intel et Microchip. Mappez les entrées et les sorties avec les registres d'E/S et AXI au niveau carte en utilisant les support packages hardware pour les cartes les plus courantes, ou définissez votre propre design de référence personnalisé.

Workflows ASIC

Concevez et vérifiez votre architecture et vos fonctionnalités hardware de haut niveau dans le contexte de votre système mixte analogique, numérique et logiciel. Générez du RTL avec une qualité de résultat (QoR) élevée ou générez du SystemC synthétisable à utiliser avec Cadence® Stratus HLS.

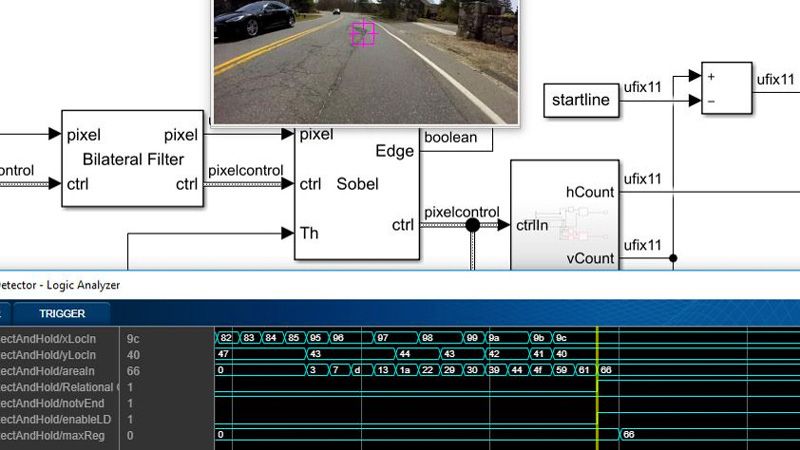

Développement d'applications

Concevez des algorithmes de communication avec des sous-systèmes et des blocs issus de Wireless HDL Toolbox, ou développez des implémentations en streaming d'algorithmes de traitement de la vision avec Vision HDL Toolbox. Implémentez des systèmes de contrôle moteur complexes à faible latence.

Exemples (communications, vision, contrôle moteur)

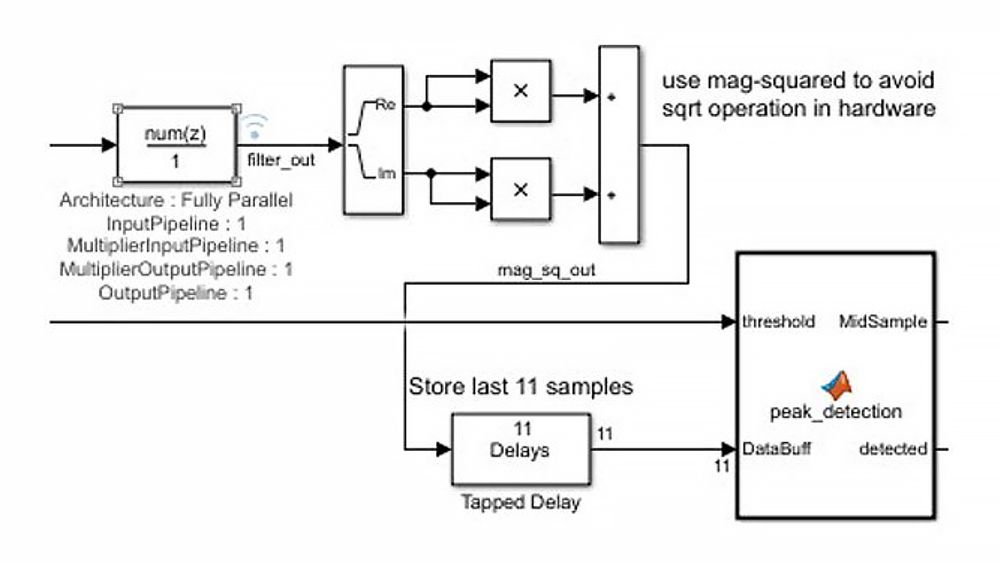

Design pour le hardware

Développez des algorithmes qui fonctionnent efficacement sur des données en streaming. Ajoutez les détails de l'architecture hardware grâce à des blocs Simulink, des blocs de MATLAB Function personnalisés et des diagrammes Stateflow compatibles avec le HDL.

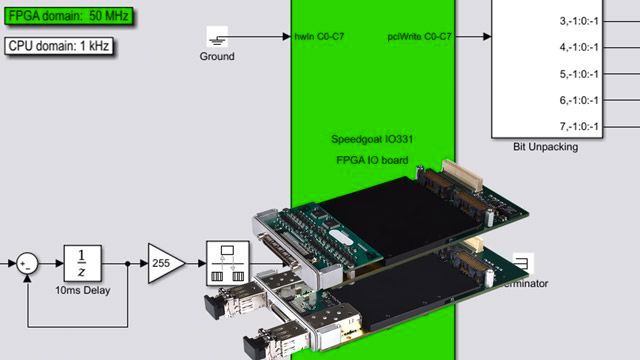

Simulation et test temps réel

Ciblez les modules d'E/S FPGA programmables Speedgoat en utilisant l'outil HDL Workflow Advisor et effectuez des simulations en utilisant Simulink Real-Time, ou utilisez des modules d'E/S FPGA supplémentaires de dSPACE et NI. Générez du code HDL à virgule flottante native afin de simplifier les workflows pour le prototypage de haute précision.

Vérification anticipée

Utilisez HDL Verifier pour vous assurer que le code RTL que vous avez généré fonctionnera comme il se doit dans son contexte système. Vérifiez le code HDL généré avec des bancs d'essai MATLAB et Simulink en utilisant la cosimulation avec les principaux simulateurs HDL. Utilisez les tests FPGA-in-the-Loop pour vérifier l'implémentation de votre design sur les cartes de développement FPGA.

Ressources produits :

« Simulink aide les architectes système et les designers hardware à communiquer. Il représente un langage commun qui nous permet d'échanger des informations, des idées et des designs. Simulink et HDL Coder nous permettent de nous concentrer sur le développement des algorithmes et l'élaboration de notre design par la simulation, plutôt que sur la vérification de la syntaxe VHDL et des règles de codage. »

Marcel van Bakel, Philips Healthcare