Vision HDL Toolbox propose des algorithmes de streaming au niveau pixel pour le design et l'implémentation de systèmes de vision sur FPGA et ASIC. La toolbox propose un framework de design qui supporte un ensemble diversifié de types d'interfaces, de tailles d'images et de fréquences d'images. Les algorithmes de Computer Vision, de traitement d'images et de vidéos de la toolbox utilisent une architecture appropriée pour les implémentations HDL.

Les algorithmes de la toolbox ont été conçus pour générer du code lisible, synthétisable en VHDL® et Verilog® (avec HDL Coder). Le code HDL généré est éprouvé sur FPGA pour des tailles d'images allant jusqu'à une résolution de 8k et pour de la vidéo à fréquence d'images élevée (HFR).

Les fonctionnalités de la toolbox sont disponibles sous forme de fonctions MATLAB, de System objects et de blocs Simulink.

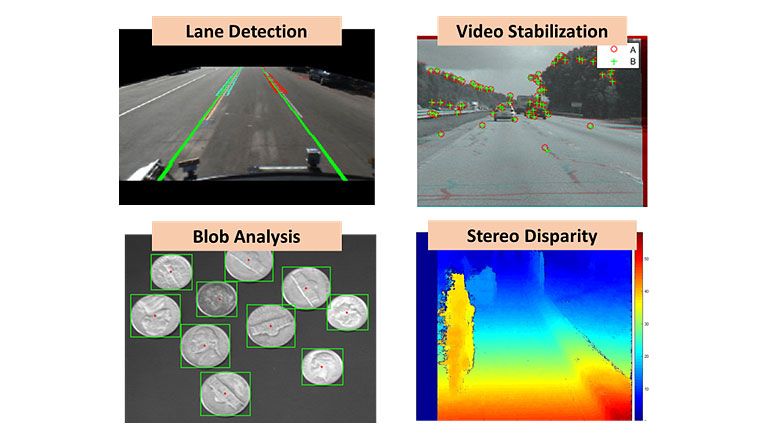

Applications de référence

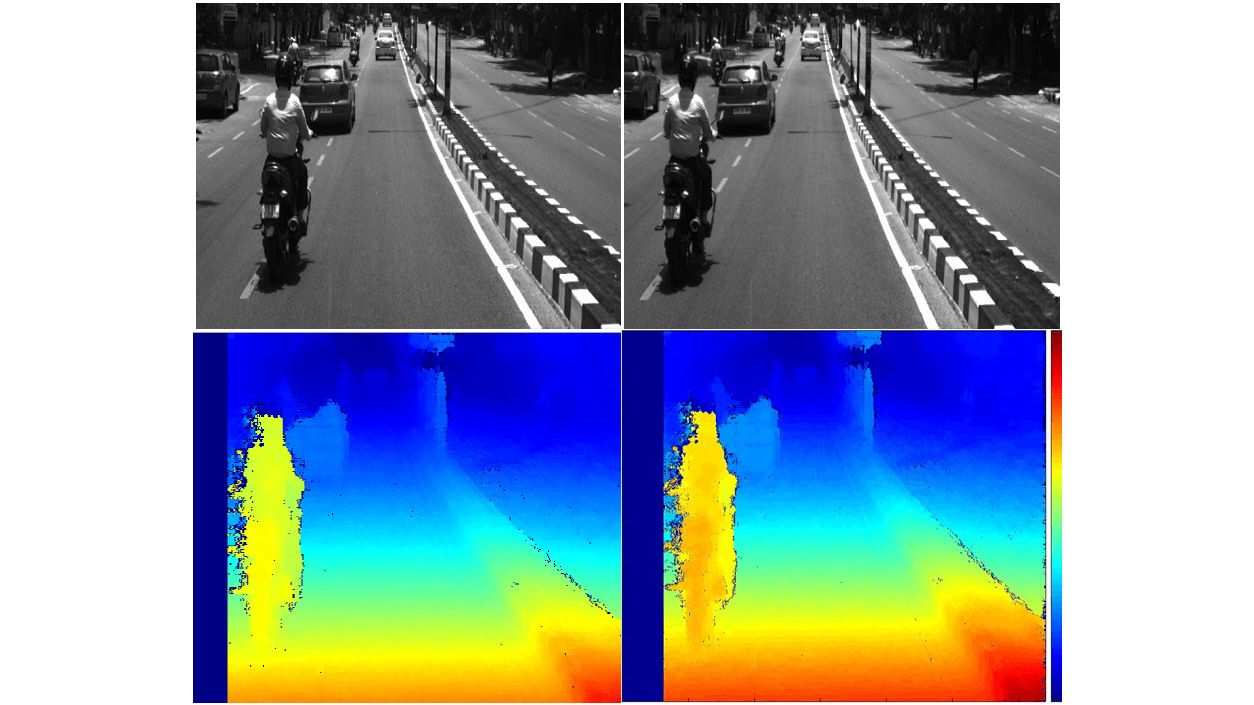

Les applications de référence constituent une base pour le design, la simulation et le déploiement d'applications de Computer Vision sur des cartes FPGA, ASIC et SoC.

Points forts du produit

Utiliser des blocs d'algorithme de vision optimisés pour le HDL

Dans la bibliothèque de la toolbox, faites votre choix parmi un éventail de blocs optimisés pour le hardware basés sur le streaming de pixels, et parmi des System objects, pour modéliser des algorithmes de traitement d'images et de vision, exigeant des calculs intensifs. Implémentez les modèles sur FPGA, ASIC et SoC.

Réaliser le design en streaming au niveau pixel

Traitez les vidéos 4k et 8k et gérez les données de streaming en entrée avec des signaux de contrôle de pixels prédéfinis, des fenêtres de région d'intérêt (ROI) et des buffers en ligne. Concevez et simulez des implémentations d'architecture hardware efficaces en utilisant le streaming unitaire ou multipixels (2, 4 ou 8 pixels par cycle) pour les algorithmes de traitement de la vision.

Démarrer avec les applications de vision de référence

Utilisez et modifiez des sous-systèmes de référence prédéfinis éprouvés sur hardware pour une implémentation optimisant les ressources des applications de Computer Vision, telles que la conduite autonome, la détection d'objets et le gestion de prise d’images par caméra.

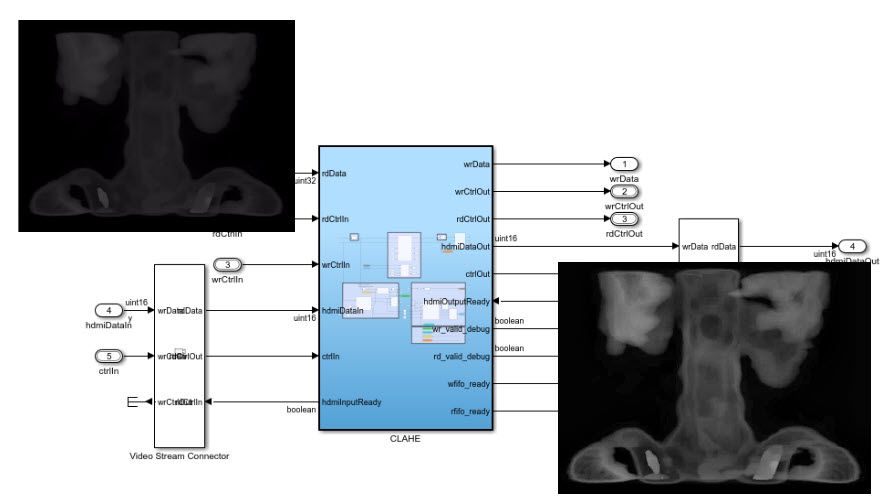

Modéliser des interfaces de mémoire externe

Utilisez les modèles Simulink pour modéliser une interface de mémoire externe pour AXI et un buffer d’images dans un design en streaming de pixel. Modélisez les accès à la mémoire en utilisant un processeur dans le cadre du codesign hardware/software et déployez des ports de sous-système sur des interfaces de mémoire physique en utilisant les fonctionnalités du SoC Blockset.

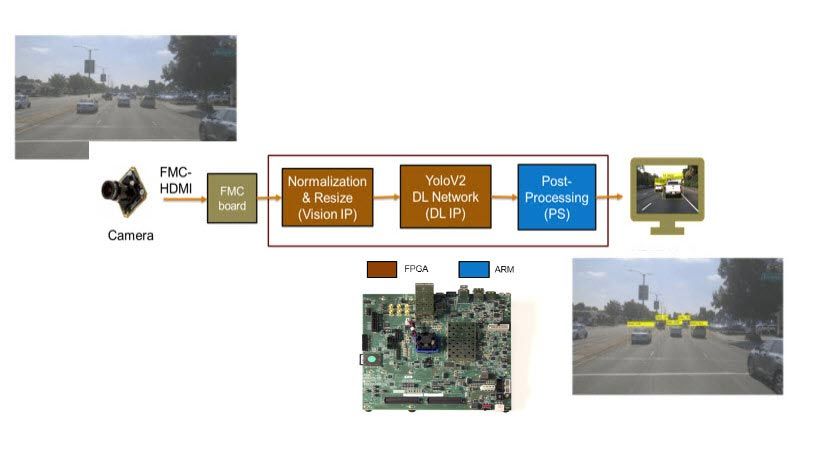

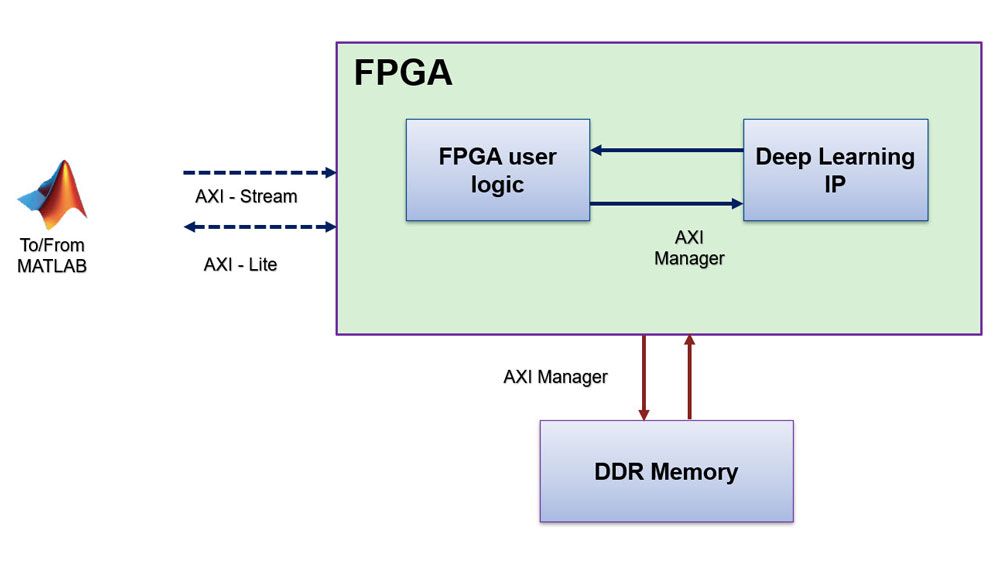

Intégrer le Deep Learning dans le design de cartes FPGA basé sur la vision

Déployez un réseau de Deep Learning YOLO v2 avec les designs de référence prédéfinis du support package sur les cartes Zynq. Utilisez une entrée de caméra enregistrée ou temps réel pour les applications de vision de détection d'objets.

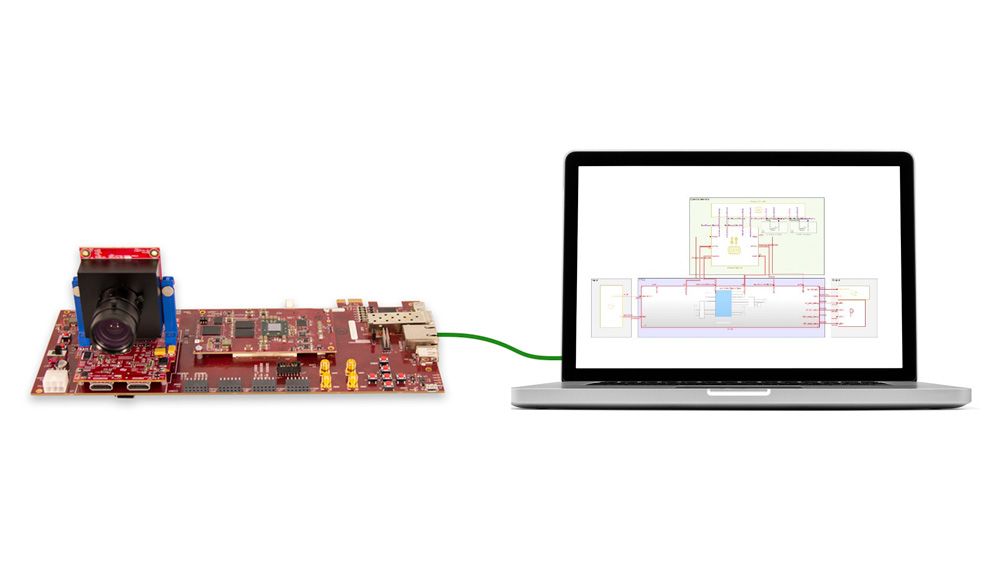

Prototyper et vérifier sur FPGA et SoC

Élaborez le design du prototype avec une entrée vidéo temps réel en utilisant le AMD Zynq Hardware Support Package et des modèles prédéfinis. Générez du code VHDL et Verilog synthétisable, indépendant de la cible avec HDL Coder pour les plateformes FPGA ou SoC supportées. Utilisez HDL Verifier pour tester et débugger vos designs hardware de vision.

Ressources produits :

« MATLAB et Simulink réduisent de moitié le temps de développement. Ces outils nous ont permis de répondre plus facilement aux besoins de notre client OEM en permettant le design de fonctions personnalisées. »

Jiyoung Jeong, LG Electronics