La traduction de cette page n'est pas à jour. Cliquez ici pour voir la dernière version en anglais.

Génération de code SIMD

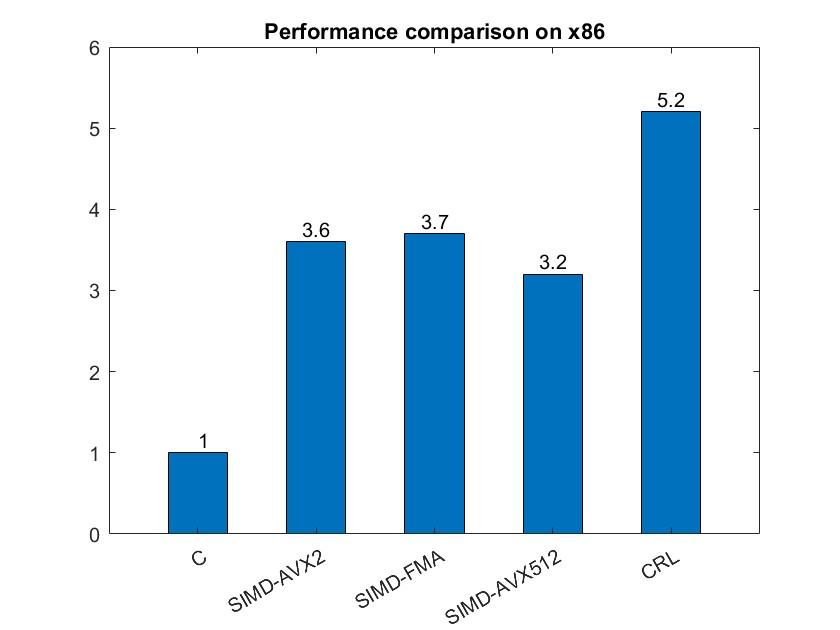

Il est possible de générer du code SIMD à partir de certains algorithmes de calcul intensif de DSP System Toolbox comme les filtres FIR et LMS. Les intrinsèques SIMD améliorent considérablement la performance du code généré à partir de ces algorithmes, au point d’égaler voire dépasser la performance de la simulation dans la plupart des cas. Le terme SIMD (Single Instruction, Multiple Data) désigne un paradigme de calcul où une instruction unique traite de multiples données. Un grand nombre de processeurs modernes disposent d’instructions SIMD qui exécutent par exemple plusieurs additions ou multiplications à la fois.

Vous pouvez générer du code SIMD avec la bibliothèque de remplacement de code DSP Intel AVX2-FMA (pour la plateforme AVX2 uniquement) ou avec le paramètre de configuration de modèle Leverage target hardware instruction set extensions (pour les processeurs Apple et ARM® Cortex®-A et pour toutes les plateformes Intel®).

Pour générer du code SIMD à partir de System objects MATLAB®, vous devez disposer de MATLAB Coder™ et de Embedded Coder®. Pour générer du code SIMD à partir de blocs Simulink® avec la bibliothèque de remplacement de code Intel AVX2, vous devez disposer de Embedded Coder. Pour générer du code SIMD à partir de blocs Simulink avec le paramètre de configuration de modèle Leverage target hardware instruction set extensions, vous devez disposer de Simulink Coder ou de Embedded Coder.

Rubriques

- System objects in DSP System Toolbox that Support SIMD Code Generation

List of System objects that support SIMD code generation.

- Simulink Blocks in DSP System Toolbox that Support SIMD Code Generation

List of Simulink blocks in DSP System Toolbox that support SIMD code generation.

- Use Intel AVX2 Code Replacement Library to Generate SIMD Code from MATLAB Algorithms

Generate high performance SIMD Code from MATLAB algorithms in DSP System Toolbox using Intel AVX2 code replacement library.

- Use Intel AVX2 Code Replacement Library to Generate SIMD Code from Simulink Blocks

Generate high performance SIMD code from Simulink blocks in DSP System Toolbox using Intel AVX2 code replacement library.

- Use Target Hardware Instruction Set Extensions to Generate SIMD Code from Simulink Blocks for Intel Platforms

Generate high performance SIMD Code from Simulink Blocks in DSP System Toolbox by using the Leverage target hardware instruction set extensions model configuration parameter.

- Use Target Hardware Instruction Set Extensions to Generate SIMD Code from Simulink Blocks for Apple silicon

Generate high performance SIMD Code from Simulink Blocks in DSP System Toolbox by using the ARM Neon technology for Apple silicon platforms.

- Use Target Hardware Instruction Set Extensions to Generate SIMD Code from Simulink Blocks for ARM Cortex-A Processors

Generate high performance SIMD Code from Simulink Blocks in DSP System Toolbox by using the Embedded Coder Support Package for ARM Cortex-A Processors.