PIL Simulation Using nSIM Simulator

Parallel processing unit (PPU) core of the Infineon® AURIX™ TC4x microcontroller is a specialized processing unit designed to speed up complex computations by using the code replacement library (CRL) technique for optimized code generation.

The nSIM instruction-set simulator provides an instruction accurate processor model for the PPU core of Infineon AURIX TC4x microcontrollers. You can use this simulator to run PIL simulations and test PPU-based application models without connecting to the hardware board. You must install the Synopsys® MetaWare toolkit to use the nSIM simulator.

Configure Simulink Model

Configure the Simulink® application model to use the nSIM PPU simulator by following these steps:

Open the PPU-based application model.

Press CTRL + E or click Model settings in the Modeling tab to open the Configuration Parameters dialog box.

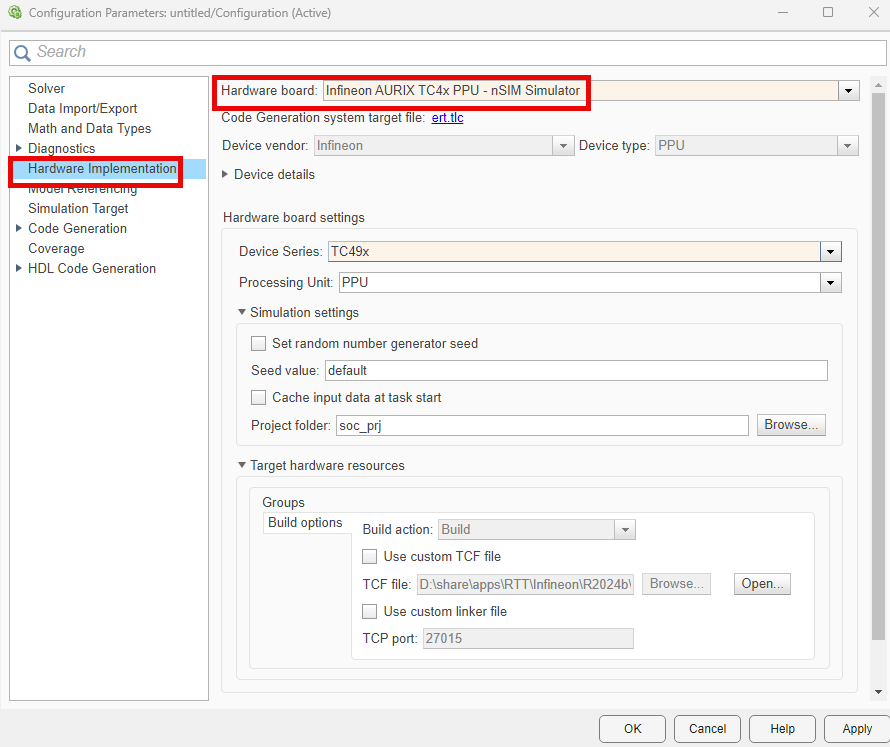

Set Hardware board to

Infineon AURIX TC4x PPU - nSIM Simulatorin the Hardware Implementation pane and click OK.

Select CRL for Optimized Code Generation

The CRL technique helps in accelerating complex computations and improving overall system efficiency by optimizing PPU runtime. For more information on CRLs available for the PPU core, see Parallel Processing Unit for Optimized Code Generation.

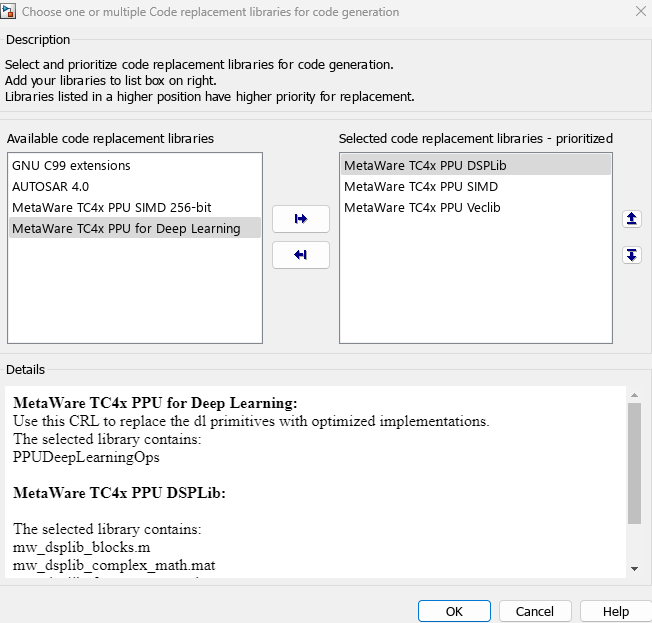

After configuring the model for the nSIM simulator, follow these steps to select a CRL from the libraries available for the Infineon AURIX PPU core:

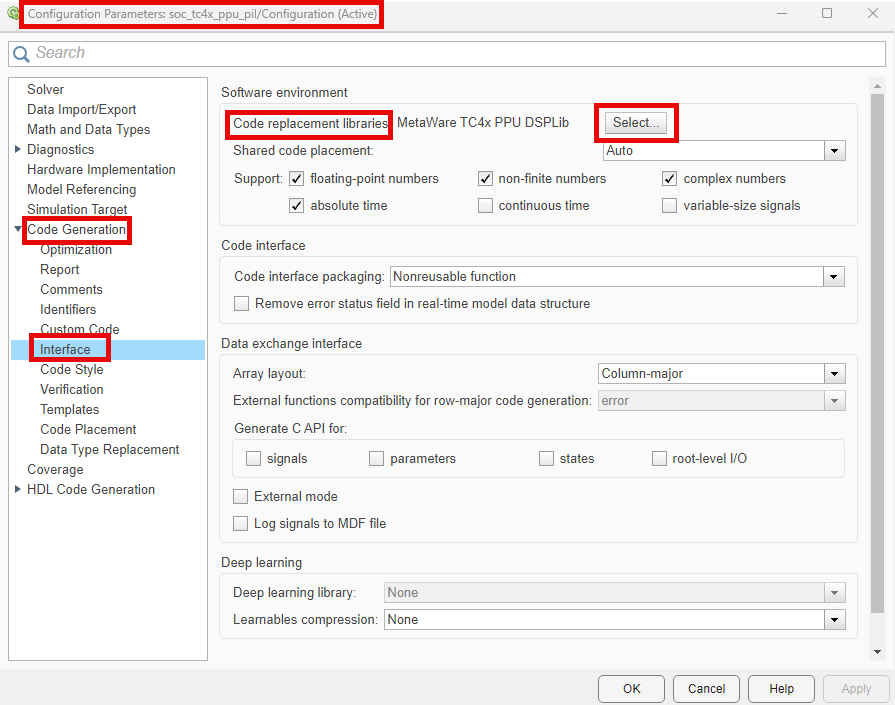

Navigate to Code Generation > Interface > Code replacement libraries in the Configuration Parameters dialog box. Click Select to view the available libraries.

Use the

and

and  buttons to add or remove a CRL.

buttons to add or remove a CRL.

The Generate and Deploy Optimized Code for Digit Classification Deep Learning Network on Infineon PPU Target example uses MetaWare TC4x PPU for Deep Learning CRL for optimized code generation and the nSIM simulator for digit classification. The example shows how to run PIL simulations and verify the numerical accuracy of the generated code against the simulation output.

Verification Using SIL/PIL Manager

Use the SIL/PIL manager to perform numerical accuracy verification of the generated code against the simulation output.

In the Simulink model, click on SIL/PIL Manager in the APPS tab to enable the SIL/PIL tab.

In the SIL/PIL tab, set SIL/PIL Mode to

Processor-in-Loop (PIL)and Mode toAutomated Verification.

Click on Run Verification. The SIL/PIL Manager application runs the model in both normal and PIL simulations and launches the Simulation Data Inspector to compare these simulation results.

Note

The PPU core does not support simulating a referenced model using PIL.

See Also

Generate and Deploy Optimized Code for Digit Classification Deep Learning Network on Infineon PPU Target | Parallel Processing Unit for Optimized Code Generation | Code Verification and Validation with PIL Using PPU | SIL and PIL Simulations | PIL Simulation Sequence | Configure and Run PIL Simulation