SoC-Based Multicore Modeling Workflow for Infineon AURIX Microcontrollers

Embedded Coder® Support Package for Infineon® AURIX™ TC4x Microcontrollers supports both time-based and event-based scheduling requirements. You can design time-based and event-based models depending on your application requirements and use them as model references in a top-level model.

The workflow includes these steps:

Create at least two unique models which can be time-based, event-based or a combination of both.

This step shows how to design a simple time-based and a event-based models configured with TriCore 0 and parallel processing unit . You can choose the number of reference models and their corresponding processing units, but each reference model must be configured to a unique processing unit.

Design Time-Based Simulink Model — Create models for algorithms that depend on time-based scheduling.

Design Event-Based Simulink Model — Create models for algorithms that depend on event-based scheduling.

Homogenous and Heterogeneous Multicore Modeling

Infineon AURIX microcontrollers contain six TriCore processing units (TriCore 0 to TriCore 5) and a parallel processing unit (PPU). Depending on the choice of these processing units for the modeling, the SoC-based multicore models can be homogenous or heterogeneous.

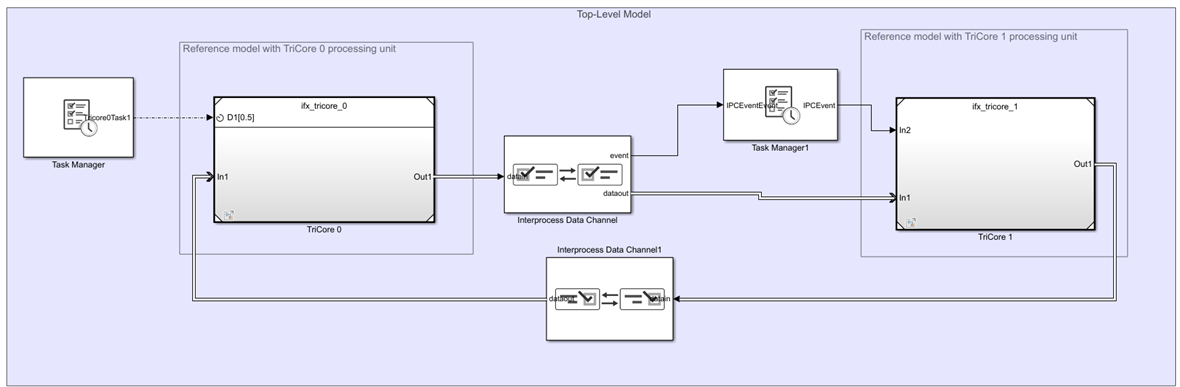

Homogenous multicore SoC models use multiple processing units which are identical in architecture, capabilities and performance. In these models, Simulink executes the generated code on the TriCore 0 and on at least one additional TriCore processing unit such as TriCore 1, TriCore 2, TriCore 3, TriCore 4, or TriCore 5.

For example, the figure shows a multicore SoC model with a time-based reference model using TriCore 0 processing unit and an event-based reference model using TriCore 1 processing unit.

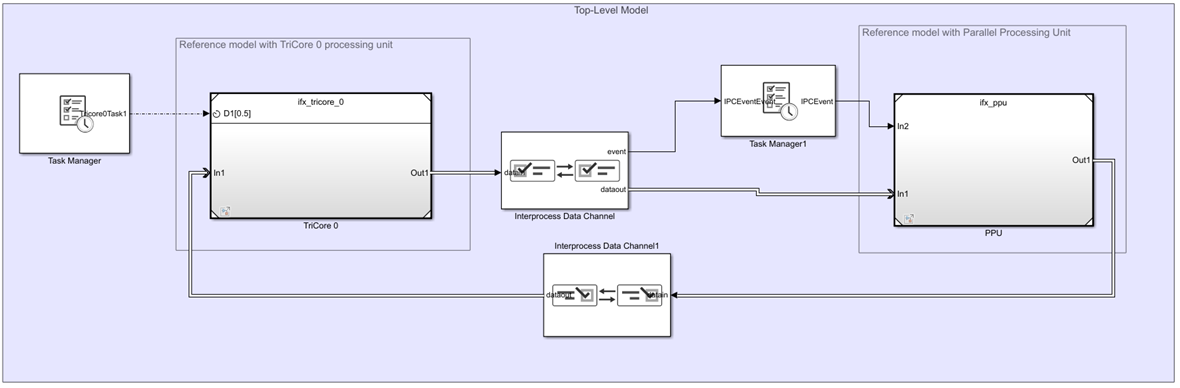

Heterogeneous multicore models use multiple processing units which differ in architecture, capabilities and performance. In these models, Simulink executes the generated code on the PPU and on at least one additional TriCore processing unit.

For example, the figure shows a multicore SoC model with a time-based reference model using TriCore 0 processing unit and an event-based reference model using PPU.

Known Limitations

PPU does not support time-based Simulink modeling.

Single executable for all homogenous cores option is not supported in Monitor & Tune (external mode) simulation.

A processing unit cannot send interrupts via the Interprocess Data Channel block to more than one other processing unit.

In a top-level model of an SoC-based multicore model, you can enable the Show event port parameter in up to eight Interprocess Data Channel blocks.