Locate Numeric Differences After Speed Optimization

This example shows how a model that contains Divide blocks might have differences in numeric results after HDL code generation. You can observe these numeric differences in the generated validation model. The validation model compares the original model with the generated model that shows the effect of block implementations and speed and area optimizations.

Reciprocal Function Model

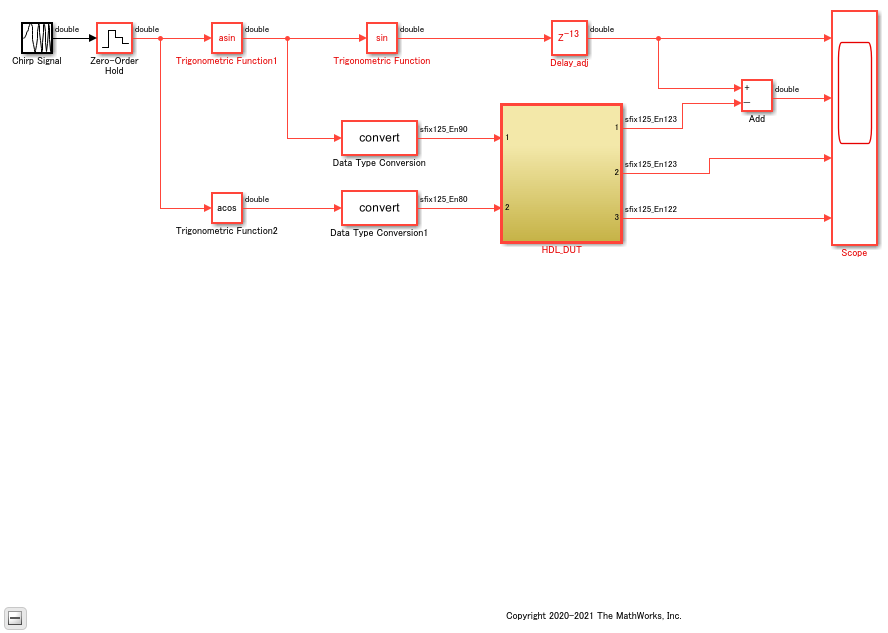

Open the model NumericDifferencesExample.

open_system('NumericDifferencesExample') set_param('NumericDifferencesExample', 'SimulationCommand', 'Update')

The model has various optimizations enabled. To see the HDL parameters saved on the model, use the hdlsaveparams function.

hdlsaveparams('NumericDifferencesExample')

%% Set Model 'NumericDifferencesExample' HDL parameters

hdlset_param('NumericDifferencesExample', 'ClockRatePipelining', 'off');

hdlset_param('NumericDifferencesExample', 'DistributedPipelining', 'on');

hdlset_param('NumericDifferencesExample', 'GenerateValidationModel', 'on');

hdlset_param('NumericDifferencesExample', 'HDLSubsystem', 'NumericDifferencesExample/HDL_DUT_LINEAR');

Inside the HDL_DUT_LINEAR subsystem, this model uses a Reciprocal block with floating-point inputs. Code generation introduces pipelines upstream of the input of the Reciprocal block.

open_system('NumericDifferencesExample/HDL_DUT_LINEAR')

Generate HDL Code and Validation Model

To see the effect of the optimization, generate HDL code and a validation model for the HDL_DUT_LINEAR subsystem by using the makehdl function.

makehdl('NumericDifferencesExample/HDL_DUT_LINEAR')

### Working on the model <a href="matlab:open_system('NumericDifferencesExample')">NumericDifferencesExample</a>

### Generating HDL for <a href="matlab:open_system('NumericDifferencesExample/HDL_DUT_LINEAR')">NumericDifferencesExample/HDL_DUT_LINEAR</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('NumericDifferencesExample', { 'HDL Code Generation' } )">NumericDifferencesExample</a> for HDL code generation parameters.

### Running HDL checks on the model 'NumericDifferencesExample'.

### Begin compilation of the model 'NumericDifferencesExample'...

### Working on the model 'NumericDifferencesExample'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 31 cycles.

### Output port 2: 31 cycles.

### Working on... <a href="matlab:configset.internal.open('NumericDifferencesExample', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_NumericDifferencesExample'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample.slx')">hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc/NumericDifferencesExample/highlightDelayAbsorption')">hdlsrc/NumericDifferencesExample/highlightDelayAbsorption.m</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/NumericDifferencesExample/highlightDistributedPipeliningBarriers')">hdlsrc/NumericDifferencesExample/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/NumericDifferencesExample/clearhighlighting.m')">hdlsrc/NumericDifferencesExample/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample_vnl')">gm_NumericDifferencesExample_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'NumericDifferencesExample'.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_add_single as hdlsrc/NumericDifferencesExample/nfp_add_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_mul_single as hdlsrc/NumericDifferencesExample/nfp_mul_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_recip_single as hdlsrc/NumericDifferencesExample/nfp_recip_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR as hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR.vhd.

### Generating package file hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR_pkg.vhd.

### Code Generation for 'NumericDifferencesExample' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR_report.html

### HDL check for 'NumericDifferencesExample' complete with 0 errors, 0 warnings, and 2 messages.

### HDL code generation complete.

When you open the HDL Check Report, you see a warning message displayed that indicates delays introduced at the inputs of the Reciprocal block, which might cause a numeric mismatch in the initial cycles when simulating the validation model.

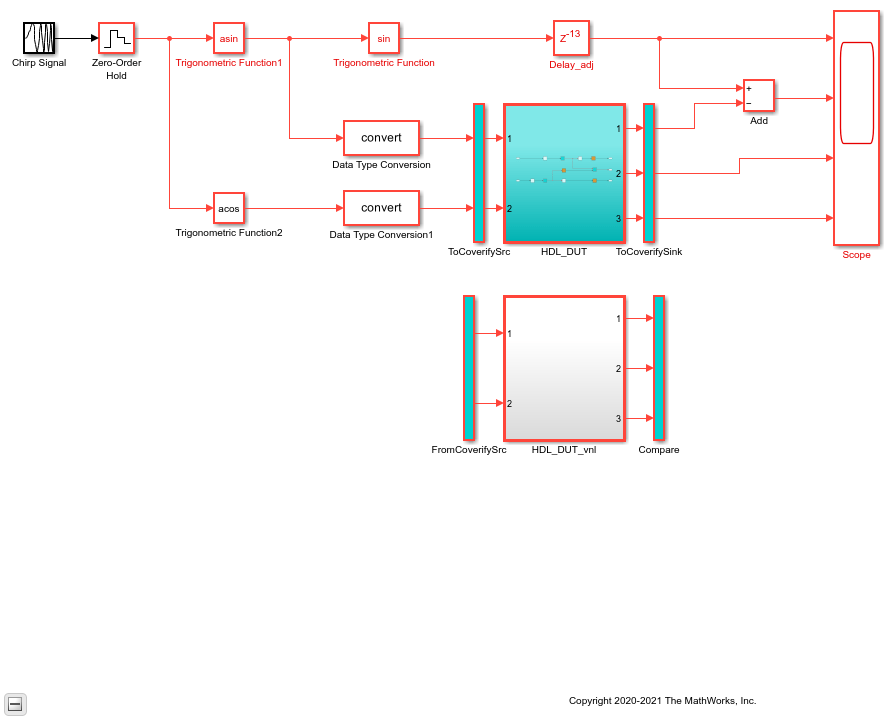

After code generation, open the verification model.

open_system('gm_NumericDifferencesExample_vnl') set_param('gm_NumericDifferencesExample_vnl', 'SimulationCommand', 'Update')

Observe Numeric Differences

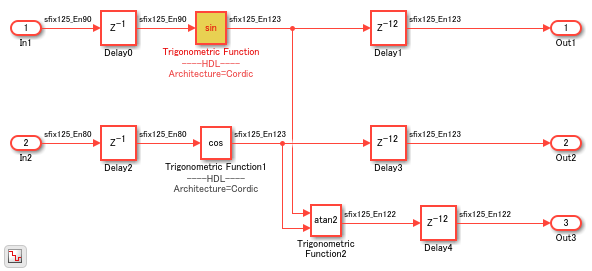

The HDL_DUT_LINEAR subsystem highlighting indicates that this subsystem is different from the subsystem in the original model HDL_DUT_LINEAR_vnl. The HDL_DUT_LINEAR subsystem is part of the generated model after HDL code generation, and shows the effect of optimizations. You also see the pipelines introduced in the block upstream of the Reciprocal block.

open_system('gm_NumericDifferencesExample_vnl/HDL_DUT_LINEAR')

When you simulate the model, you see assertions detected in the initial cycles of simulation, which indicates a numeric mismatch. The mismatch is caused by pipelines introduced upstream of the Reciprocal block.

sim('gm_NumericDifferencesExample_vnl'); open_system('gm_NumericDifferencesExample_vnl/Compare/Assert_out/compare: out')

Warning: Division by zero in

'gm_NumericDifferencesExample_vnl/HDL_DUT_LINEAR_vnl/Reciprocal'

Suggested Actions:

• - Suppress

Warning: Division by zero in

'gm_NumericDifferencesExample_vnl/HDL_DUT_LINEAR/Reciprocal_recip/Reciprocal_recip'

Suggested Actions:

• - Suppress

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 31

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 32

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 33

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 34

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 35

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 36

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 37

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 38

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 39

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 40

Warning: Assertion detected in

'gm_NumericDifferencesExample_vnl/Compare/Assert_out/AssertEq' at time 41

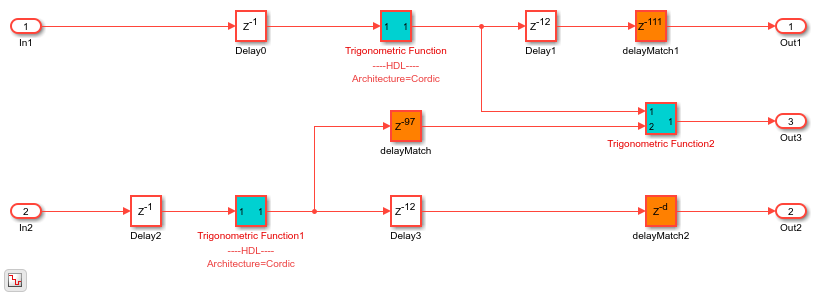

Address Numeric Differences

If your design requires numerical integrity even during initialization cycles, at the potential cost of lower clock frequency, you can set the Pipeline distribution priority parameter to Numerical Integrity. If this does not fix the mismatch, you can turn off input pipelining from any blocks upstream of the delay balance blocker.

hdlset_param('NumericDifferencesExample/HDL_DUT_LINEAR/Add','LatencyStrategy','Zero') makehdl('NumericDifferencesExample/HDL_DUT_LINEAR') sim('gm_NumericDifferencesExample_vnl'); open_system('gm_NumericDifferencesExample_vnl/Compare/Assert_out/compare: out')

### Working on the model <a href="matlab:open_system('NumericDifferencesExample')">NumericDifferencesExample</a>

### Generating HDL for <a href="matlab:open_system('NumericDifferencesExample/HDL_DUT_LINEAR')">NumericDifferencesExample/HDL_DUT_LINEAR</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('NumericDifferencesExample', { 'HDL Code Generation' } )">NumericDifferencesExample</a> for HDL code generation parameters.

### Running HDL checks on the model 'NumericDifferencesExample'.

### Begin compilation of the model 'NumericDifferencesExample'...

### Working on the model 'NumericDifferencesExample'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 20 cycles.

### Output port 2: 20 cycles.

### Working on... <a href="matlab:configset.internal.open('NumericDifferencesExample', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_NumericDifferencesExample'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample.slx')">hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample.slx</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/NumericDifferencesExample/highlightDistributedPipeliningBarriers')">hdlsrc/NumericDifferencesExample/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/NumericDifferencesExample/clearhighlighting.m')">hdlsrc/NumericDifferencesExample/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/NumericDifferencesExample/gm_NumericDifferencesExample_vnl')">gm_NumericDifferencesExample_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'NumericDifferencesExample'.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_add_single as hdlsrc/NumericDifferencesExample/nfp_add_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_mul_single as hdlsrc/NumericDifferencesExample/nfp_mul_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR/nfp_recip_single as hdlsrc/NumericDifferencesExample/nfp_recip_single.vhd.

### Working on NumericDifferencesExample/HDL_DUT_LINEAR as hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR.vhd.

### Generating package file hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR_pkg.vhd.

### Code Generation for 'NumericDifferencesExample' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex48041239/hdlsrc/NumericDifferencesExample/HDL_DUT_LINEAR_report.html

### HDL check for 'NumericDifferencesExample' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

Warning: Division by zero in

'gm_NumericDifferencesExample_vnl/HDL_DUT_LINEAR_vnl/Reciprocal'

Suggested Actions:

• - Suppress

Warning: Division by zero in

'gm_NumericDifferencesExample_vnl/HDL_DUT_LINEAR/Reciprocal_recip/Reciprocal_recip'

Suggested Actions:

• - Suppress