Generate Cross-Platform UVM Components

Generate Universal Verification Methodology (UVM) components for a direct transition from your Simulink® environment to a UVM framework. HDL Verifier™ exports Simulink subsystems as generated C code inside UVM components with a direct programming interface (DPI). You can integrate these generated components into your existing UVM environment. You can also use the generated UVM testbench to test an HDL DUT by replacing the generated behavioral DUT with your detailed HDL design.

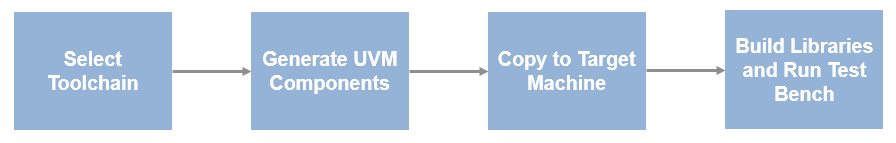

When you generate the UVM components from a Windows® 64 host machine, you can also build the component libraries and run the simulation on a Linux® operating system. If your target and host are not the same, you must port and build the shared libraries or HDL simulator projects manually. You cannot port a UVM components generated on a Linux machine to any other operating system.

This workflow supports the Cadence® Xcelium™, Siemens® ModelSim™, Siemens Questa™, and Synopsys® VCS® HDL simulators.

Note

This feature requires the ASIC Testbench for HDL Verifier add-on.

Select Target Toolchain

When your target machine uses the same operating system as your host, you can select an installed compiler or request that the tools find a compiler automatically. If you want to generate a simulator project, or if you have no other compilers installed, select an HDL simulator for the same operating system as the host. However, if your target operating system is different from the host, you must select a target simulator and operating system.

Because UVM generation utilizes the technology for generating SystemVerilog DPI, you must first select a supporting system target file. Open your model,

and on the Apps tab, click HDL Verifier. Select

DPI Component Generation on the left pane, and on the HDL

Verifier tab, click C Code Settings. The

Configuration Parameters dialog box opens on the Code

Generation pane. Under Target selection, for System target file, click Browse, and then

select systemverilog_dpi_grt.tlc from the list.

Alternatively, if you have the Embedded Coder® product, you can select target systemverilog_dpi_ert.tlc.

This target enables you to access additional code generation options when you select

Code Generation from the left pane of the

Configuration Parameters dialog box. For an example of UVM

generation, see Generate Parameterized UVM Testbench from Simulink.

Then, under Build process, select a target Toolchain. This option specifies the target simulator and operating system where you run simulations. The supported cross-product toolchains are:

Cadence Xcelium (64-bit Linux)Siemens Questa/ModelSim (64-bit Linux)Synopsys VCS (64-bit Linux)

To build a shared library for a different operating system, you must select one of the simulator options. You can then build the library on your target machine.

Generate Component

Use the uvmbuild function

to generate the structure of UVM components. The function generates SystemVerilog DPI (SV-DPI) components from your DUT, sequence, and scoreboard subsystems, as

well as optional SV-DPI components for driver, monitor or predictor subsystems if your model

includes them. The function also generates the UVM testbench from your Simulink model. The function packages the artifacts of DPI generation in a directory

named uvm_build.zip in your working directory, that includes these two directories:

top_model_dpi_componentstop_model_uvm_testbench

Where top_model

You can change the default directory by setting the buildDirectory

property in the uvmcodegen.uvmconfig configuration object.

Copy to Target Machine

To use your generated components on a different operating system, you must copy the generated package file to the target machine, unzip it, and build the component libraries there.

Copy the generated

uvm_build.zipfile from the host machine to the target machine. The.zipfile is located in the same folder as your model. The.zipfile includes the ModelSim file with the.doextension or the VCS or Xcelium file with the.shextension.Unzip the file into a folder of your choice.

Build Libraries and Run Testbench

When you generate the components on the host machine, the libraries are built for that operating system. To port the components to a different operating system, you must build the components manually on the target machine. To build the project and run the testbench in the HDL simulator, find your HDL simulator in the table and follow the instructions.

| HDL Simulator | Instructions |

|---|---|

| ModelSim or Questa |

|

| VCS |

|

| Xcelium |

|

Limitations

Cross-platform UVM generation does not support model referencing when the reference subsystem in your Simulink model has a Test Assessment (Simulink Test) block.