Peripheral Management

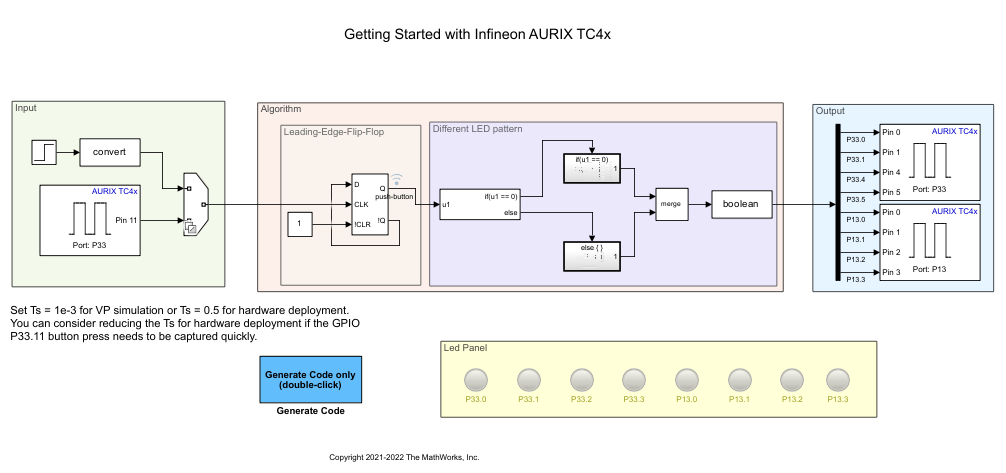

Configure Infineon®

AURIX™ TC4x microcontrollers using blocks, peripheral app and

configuration parameter settings

Before communicating with target hardware, first apply block settings, hardware configuration parameters and peripheral app settings.

Blocks

Tools

| SoC Builder | Build, load, and execute multicore application models on Infineon AURIX TC4x hardware boards (Since R2024b) |

| Hardware Mapping | Map tasks and peripherals in a model to hardware board configurations (Since R2022b) |

| Digital Port Read Peripheral Configuration | Map Digital Port Read peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| Digital Port Write Peripheral Configuration | Map Digital Port Write peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| Tasks | Map tasks in the Infineon AURIX to interrupt service routines on the hardware board (Since R2022b) |

| Encoder Peripheral Configuration | Map encoder peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| PWM Peripheral Configuration | Map PWM peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| QSPI Peripheral Configuration | Map QSPI peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| DSADC Peripheral Configuration | Map DSADC peripherals in Infineon AURIX model to peripheral registers in MCU (Since R2023b) |

| TMADC Peripheral Configuration | Map TMADC peripherals in the Infineon AURIX model to peripheral registers in the MCU (Since R2022b) |

| SENT Configuration | Map data transfer over SENT protocol in the Infineon AURIX model to peripheral registers in the MCU (Since R2023b) |

| FCC Peripheral Configuration | Map FCC peripherals in the model to peripheral registers in MCU (Since R2024a) |

| Resolver Peripheral Configuration | Map resolver peripherals in model to peripheral registers in MCU (Since R2024a) |

| CDSP Peripheral Configuration | Map CDSP peripherals in model to peripheral registers in the MCU (Since R2024a) |

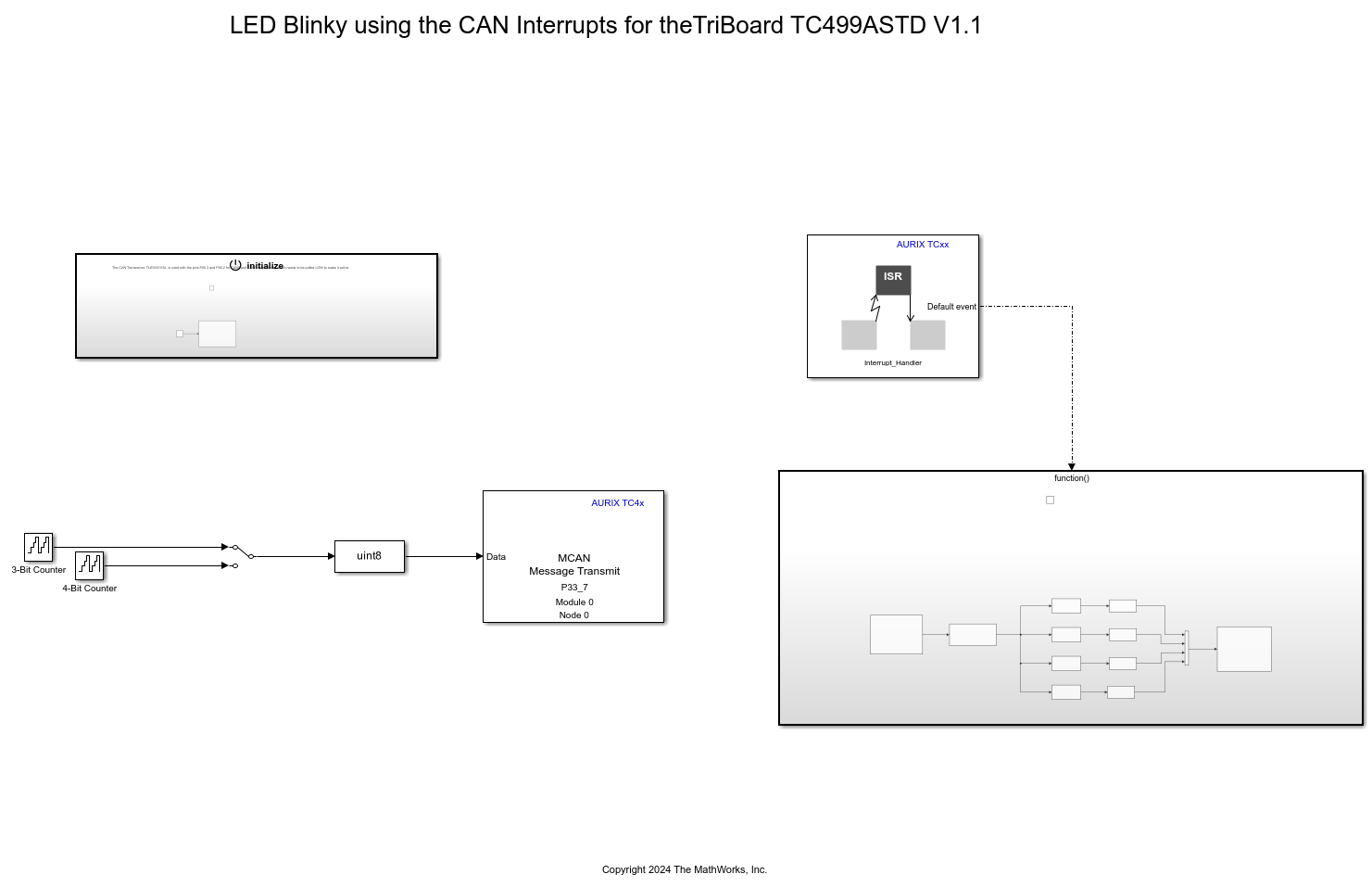

| MCAN Transmit Peripheral Configuration | Map peripherals of MCAN Transmit block in the model to peripheral registers in MCU (Since R2024b) |

| MCAN Receive Peripheral Configuration | Map MCAN Receive peripherals in the model to the peripheral registers in MCU (Since R2024b) |

Model Settings

Topics

- Run Model on Virtual Prototyping (VP)

Run your model on virtual prototyping without the hardware using the Synopsys Virtual Prototyping (VP) Virtualizer.

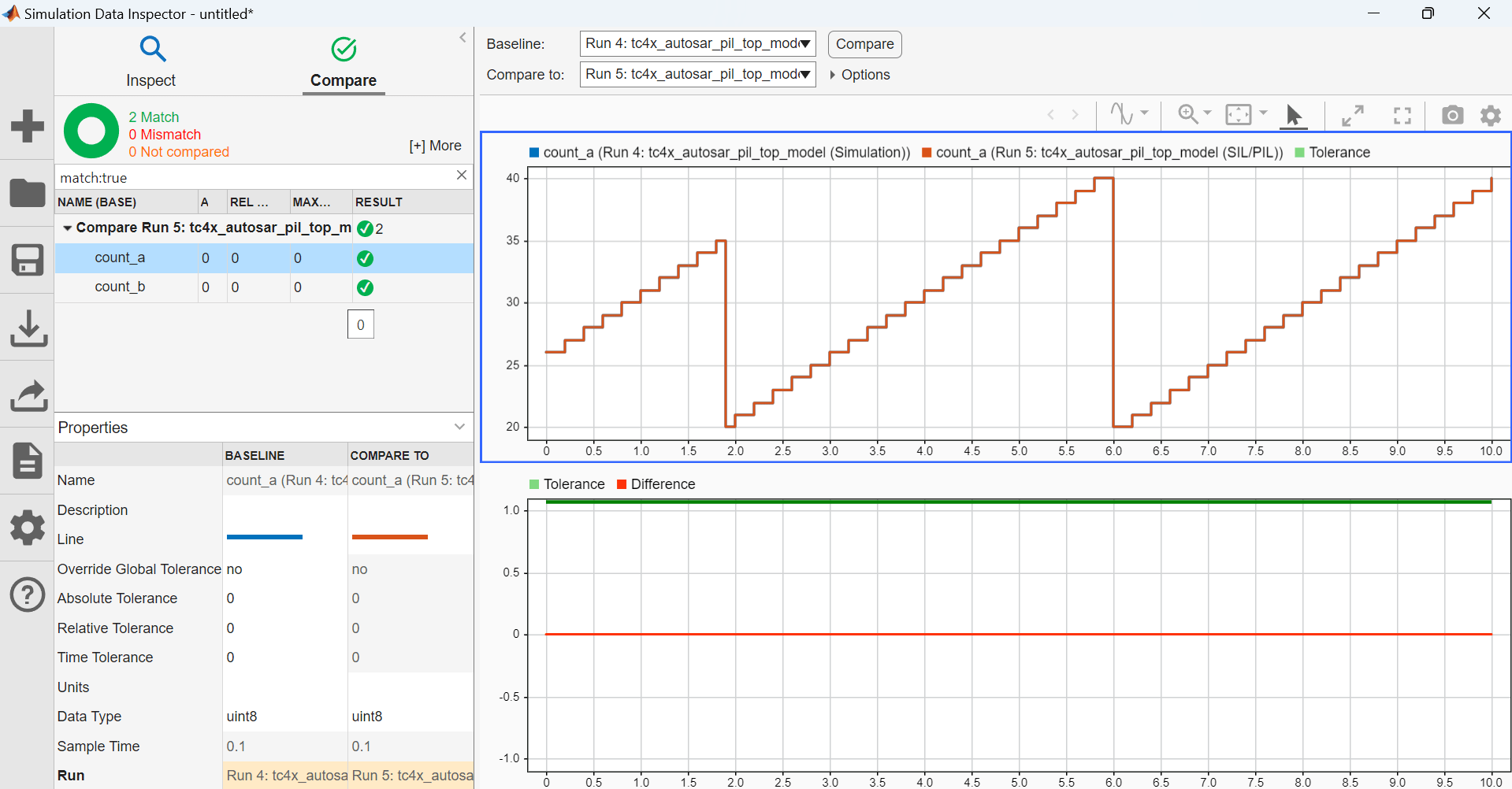

- PIL Simulation Using nSIM Simulator

Run PIL simulations and test PPU based application models using nSIM simulator.