LTE OFDM Demodulator

Demodulate time-domain OFDM samples and return LTE resource grid

Libraries:

Wireless HDL Toolbox /

Modulation

Description

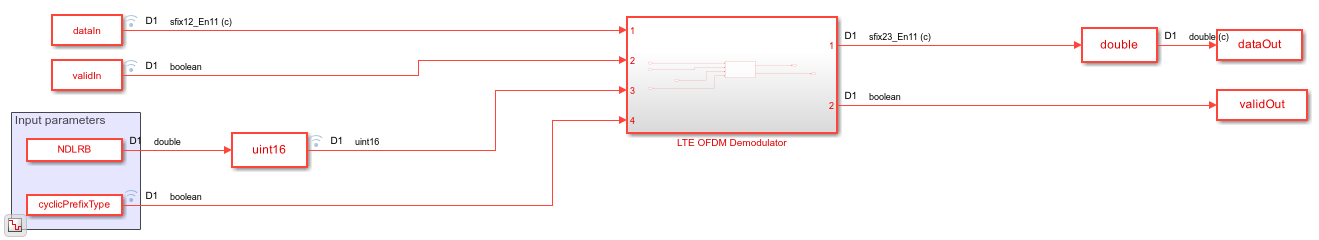

The LTE OFDM Demodulator block implements an algorithm for demodulating LTE signals specified by LTE standard TS 36.212 [1]. The block returns the LTE resource grid that is used for cell ID detection, master information block (MIB) recovery, system information block (SIB)1 recovery, and further decoding.

You can select the number of downlink resource blocks (NDLRB) and choose either normal or extended cyclic prefix (CP), as described in the LTE standard. The block implements a CP fraction to support windowed LTE transmission and provides a parameter to configure the location of prefix removal.

The block provides an interface and architecture suitable for HDL code generation and hardware deployment.

The block accepts input data either at maximum rate of 30.72 MHz, or at a sample rate corresponding to NDLRB. The input sampling rates for NDLRB 6, 15, 25, 50, 75, and 100 are 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 30.72 MHz, and 30.72 MHz, respectively. The block uses a 2048-point fast fourier transform (FFT) for all values of NDLRB and returns the number of resource grid samples needed for the selected NDLRB. By default, the block excludes the direct current (DC) carrier.

The latency from the first input sample to the first output sample depends on your selection of the NDLRB and type of cyclic prefix, as shown in this table.

| Maximum Sample Rate | Corresponding to NDLRB Sample Rate | |||

|---|---|---|---|---|

| NDLRB | Latency — Normal CP | Latency — Extended CP | Latency — Normal CP | Latency — Extended CP |

| 6 | 5295 | 5647 | 6654 | 6676 |

| 15 | 5241 | 5593 | 6520 | 6564 |

| 25 | 5181 | 5533 | 6660 | 6748 |

| 50 | 5031 | 5383 | 6700 | 6876 |

| 75 | 4881 | 5233 | 6930 | 7282 |

| 100 | 4731 | 5083 | 6780 | 7132 |

Examples

LTE OFDM Demodulation of Streaming Samples

Use LTE OFDM Demodulator block to return LTE resource grid from streaming samples.

Reset and Restart LTE OFDM Demodulation

Recover LTE OFDM Demodulator block from unfinished LTE cell.

Modulate and Demodulate LTE Resource Grid

Modulate and demodulate LTE resource grid samples.

Ports

Input

Input data, specified as a signed real or complex number.

The software supports double and

single data types for simulation, but not for HDL code generation.

Data Types: single | double | int8 | int16 | int32 | signed fixed point

Complex Number Support: Yes

Control signal that indicates when the sample from the

data input port is valid. When this value is

1 (true), the block captures the values on the

data input port. When this value is

0 (false), the block ignores the input

data samples.

Data Types: Boolean

Number of downlink resource blocks, specified as 6,

15, 25, 50,

75, or 100. NDLRB must be one

of these six values specified by LTE standard TS 36.212 [1].

The block samples this port at the start of each subframe and ignores

any changes within a subframe.

Dependencies

To enable this port, set the NDLRB source

parameter to Input port.

Data Types: uint8 | uint16 | uint32 | fixdt(0,K,0), K >= 7 | single | double

Type of CP, specified as a Boolean scalar. When this value is

0 (false), the block selects normal CP. When this value is

1 (true), the block selects extended CP. The block samples this

port at the start of each subframe and ignores any changes within a subframe.

Dependencies

To enable this port, set the Cyclic prefix source parameter

to Input port.

Data Types: Boolean

Clears internal state, specified as a Boolean

scalar. When this value is 1 (true), the block stops

the current calculation and clears all internal states. When this value

is 0 (false), and the valid

input value is 1 (true), the block begins a new

subframe.

Dependencies

To enable this port, select the Enable reset input port parameter.

Data Types: Boolean

Output

Output data, returned as a signed real or complex number. The data type is the same as the data type of the input data port. When you clear the Divide butterfly outputs by two parameter, the output word length increases by 11 bits to avoid overflow.

Data Types: single | double | int8 | int16 | int32 | signed fixed point

Complex Number Support: Yes

Control signal that indicates when the data

output port is valid. The block sets this value to 1

(true) when the resource grid samples are available on the

data output port. When Remove DC

subcarrier is selected, this value is set to

0 (false) at the center of the output samples to

exclude the DC carrier.

Data Types: Boolean

Control signal that indicates when the block is ready for new input

data. When this value is 1 (true), the block accepts

input data in the next time step. When this value is

0 (false), the block ignores input data in the

next time step.

Dependencies

To enable this port, set the Input data sample

rate parameter to Match input data

sample rate to NDLRB.

Data Types: Boolean

Parameters

Main

You can set NDLRB with an input port or by selecting a value for the

parameter. To enable the NDLRB parameter, select

Property. To enable the

NDLRB port, select Input

port.

Number of downlink resource blocks, specified as 6,

15, 25, 50,

75, or 100. NDLRB must be one

of these six values specified by LTE standard TS 36.212 [1].

Dependencies

To enable this parameter, set the NDLRB

source parameter to

Property.

You can set the cyclic prefix by selecting a parameter value or using

an input port. To enable the Cyclic prefix type

parameter, select Property. To enable the

cyclicPrefixType port, select

Input port.

Type of cyclic prefix, specified as Normal

or Extended.

Dependencies

To enable this parameter, set the Cyclic prefix

source parameter to

Property.

Cyclic prefix fraction, specified as a value from 0 to 1, inclusive. This parameter specifies the percentage of CP samples that the block removes from the start of the OFDM symbol. The block shifts the remaining CP samples to the end of the OFDM symbol.

When this parameter is 0.55, the block removes 55%

of the CP from the beginning of the symbol, and shifts 45% to the end of

the symbol. When you set this parameter to 1, the

block removes 100% of the CP from the start of the OFDM symbol, and does

not shift any samples to the end.

CP fraction provides windowed LTE transmission

support. When a transmitter applies windowing, symbols are cyclically

extended and overlapped. In a receiver design, the best location to

remove the prefix and extract the symbol depends on windowing settings

at the transmitter. For more information on windowing for an LTE

transmitter, see the Algorithms section of lteOFDMModulate (LTE Toolbox)

function.

When you select this parameter, the block excludes the DC subcarrier

in the resource grid output. The DC subcarrier is present at the center

of the 12×NDLRB subcarriers. The block excludes the DC subcarrier by

setting the valid signal low

(false) for the center cycle of the output

subcarriers.

Select this parameter to enable the reset port on the block icon.

This parameter specifies the type of sample rate to select for the input data.

To provide an input data sample rate of 30.72 MHz, select

Use maximum input data sample rate.To provide an input data sample rate based on the NDLRB parameter, select

Match input data sample rate to NDLRB. The input sampling rates for NDLRB values6,15,25,50,75, and100are 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 30.72 MHz, and 30.72 MHz, respectively.

For more information, see Data Rate Controller.

FFT Parameters

This parameter controls the scaling option of the FFT block inside the LTE OFDM Demodulator.

When you select this parameter, the FFT implements an overall 1/N scale factor by dividing the output of each butterfly multiplication by two. This adjustment keeps the output of the FFT in the same amplitude range as its input. If you disable this parameter, the block avoids overflow by increasing the word length by one bit after each butterfly multiplication.

This parameter specifies the type of rounding mode for internal

fixed-point calculations. For more information about rounding modes, see

Rounding

Modes. When the input is any integer data type or fixed-point

data type, the FFT algorithm uses fixed-point arithmetic for internal

calculations. This parameter does not apply when the input is of data

type single or double. Rounding

applies to twiddle-factor multiplication and scaling operations.

Algorithms

The LTE OFDM Demodulator block operation sequence is carried over using these blocks: Data Rate Controller, CP Prefix Removal, Sample Repeater, FFT Shift, FFT, and Resource Grid Selection. The Data Rate Controller block helps in controlling the input data rate by generating a ready signal. The CP Removal block removes the part of the CP at the start of a symbol and the remainder of the CP at the end of the symbol. The Sample Repeater block repeats the samples based on the NDLRB values. The block repeats the samples until they form 2048 samples and converts the input data rate to the maximum rate supported by LTE. The FFT Shift block performs a time-domain FFT shift. The FFT block converts the frequency-domain signal to a time-domain signal. The Resource Grid Selection block extracts the resource grid elements based on the NDLRB and the input data sample rate, and provides the demodulated output. The parameters shown in this figure configure the behavior of the block.

The block accepts input data either at maximum rate of 30.72 MHz, or at a sample rate corresponding to NDLRB. The input sampling rates for NDLRB values 6, 15, 25, 50, 75, and 100 are 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 30.72 MHz, and 30.72 MHz, respectively.

When you set the Input data sample rate parameter to

Use maximum input data sample rate, the block

operates based on the demodulation parameters (NDLRB and

CP prefix type) and provides output data along with an

output valid signal to the next block.

When you set the Input data sample rate parameter to

Match input data sample rate to NDLRB, the block

generates an output ready signal and controls the input at a

rate with respect to the NDLRB. The block accepts data samples with respect to the

NDLRB when the ready signal is 1

(true).

This figure shows a Logic Analyzer waveform of the ready

signal generation for a continuous input when NDLRB is

6 and CP prefix type is

Normal, having FFT length as 128 and CP length as

10.

numHigh = FFT length + CP length = 128 +10 = 138 clock cycles.

numLow = Maximum FFT length + Maximum CP length - (numHigh) = 2048 + 160 - (138) = 2070 clock cycles.

This figure shows a Logic Analyzer waveform of the ready

signal generation for a discrete input with 1 (high) for 16 clock

cycles when NDLRB is 6 and

CP prefix type is Normal, having

FFT length as 128 and CP length as 10.

numHigh = (FFT length + CP length -1) * Maximum FFT length / FFT length + 1 = (128 +10 -1) * 16 + 1 = 2193 clock cycles.

numLow = Maximum FFT Length + Maximum CP Length - (numHigh) = 2048 + 160 - (2193) = 15 clock cycles.

This block supports windowed LTE transmission by implementing fractional cyclic prefix removal. Windowing reduces out-of-band emissions. A transmitter performs windowing by overlapping the tail of each OFDM symbol with the head of the next OFDM symbol. A receiver must avoid these overlapped samples in the FFT calculation. Fractional CP solves this problem by removing part of the CP at the start of a symbol and the remainder of the CP at the end of the symbol. Implementing a CP-fraction algorithm also makes the LTE OFDM Demodulator block less sensitive to timing offset.

The Cyclic prefix type parameter controls whether the block expects normal or extended CP. When the block operates at a maximum sample rate of 30.72 MHz, it assumes that each symbol is 2048 samples plus the cyclic prefix size associated with that rate. When using normal CP, the prefix of the first symbol in each slot has 160 samples, while subsequent symbols have a prefix of 144 samples. The extended CP has 512 samples.

When the block operates at sample rates with respect to the NDLRB value, for example, if the NDLRB is 6, the block receives 128 samples plus the cyclic prefix size associated with that rate. When using normal CP, the prefix of the first symbol in each slot has 10 samples, while subsequent symbols have a prefix of nine samples. The extended CP has 32 samples.

The block handles the CP in two stages. First, the block calculates the number of CP samples to remove, Nr, and removes those samples from the input samples. Next, it calculates the number of samples to shift, Ns, and shifts those samples to the end of OFDM symbol in the time domain. These two segments together make up the total cyclic prefix length, Ncp = Ns + Nr.

The CP fraction parameter controls how many samples the block

removes at the beginning of the symbol. The block shifts the remainder of the cyclic

prefix from the start of the symbol to the end of the symbol. The block quantizes

CP fraction to fi(0,11,10). To achieve

an integer number of samples, the block calculates Nr =

floor (Ncp * CP

fraction).

The Logic Analyzer waveform shows the control signals for the two stages of CP

removal. The block is configured for a normal CP, so the CP of the first symbol is

160 samples. The CP for subsequent symbols is 144 samples. The CP

fraction is 0.55.

In stage one, the block sets the internal valid signal to

0 (false) to exclude the first

Nr samples of the symbol. For the first symbol,

Nr = 88. Manipulation of the valid

signal also excludes the final Ns samples, which are replaced by

the shifted samples in the next stage. For the first symbol, Ns =

72. In stage two, the block writes the Ns samples to a RAM, and

then reads and returns these samples at the end of the symbol. The block shifts the

internal valid signal to include the shifted samples in their

new location. The result is 2048 samples, properly aligned in the time domain in

preparation for an FFT.

For the second symbol, with a cyclic prefix of 144 samples, Nr = 80 and Ns = 64.

For more information on LTE transmitter windowing, see the Algorithms section of

the lteOFDMModulate (LTE Toolbox) function.

As the LTE OFDM Demodulator block uses a maximum FFT length of 2048. So, when the input samples corresponding to the actual FFT length are provided, the Sample Repeater block repeats the samples until it forms 2048 samples. For this operation, the block buffers the input samples first, and then repeats the samples based on the NDLRB value. This repetition mechanism helps avoid scaling at the FFT block input. For example, if the NDLRB is 6, each OFDM symbol consists of 128 samples. The block converts these 128 samples to 2048 samples by repeating them 16 times. After the block generates 2048 data samples, it sends data and valid signals to the next block.

Conventionally, receivers perform FFT shift in the frequency domain. However, this method requires memory and introduces latency related to the size of the FFT. Instead, a receiver can execute the same operation in the time domain using the frequency shifting property of Fourier transforms. Shifting a function in one domain corresponds to a multiplication by a complex exponential function in the other domain. To reduce hardware resources and latency, this block performs the FFT shift by multiplying the time-domain samples by a complex exponential function.

These equations describe an FFT shift. The equation for an N-point FFT is

For an FFT shift of N/2 carriers in either direction, substitute , resulting in

This equation simplifies to

Since is equivalent to , and , this equation simplifies to

The final equation shows that an FFT shift in the time domain simplifies to multiplication by (-1)n. Therefore, the block implements the FFT shift by multiplying the time-domain samples by either +1 or –1.

The output of the FFT shift subsystem is fed to an FFT block. The sample rate of the time-domain samples must be 30.72 MHz. The block calculates a 2048-point FFT for all NDLRB values.

The Divide butterfly outputs by two parameter controls whether the FFT implements an overall 1/N scale factor by dividing the output of each butterfly multiplication by two. This adjustment keeps the output of the FFT in the same amplitude range as its input. When you disable scaling (default), the block avoids overflow by increasing the word length by one bit after each butterfly multiplication.

This part of the algorithm selects the appropriate number of subcarriers based on the NDLRB. Out of 2048 subcarriers, the block selects the center 12xNDLRB subcarriers for output.

If the Remove DC subcarrier parameter is selected, the block

excludes the DC subcarrier from the final resource grid output. The block excludes

the DC subcarrier by setting the valid signal to

0 (false) for the center cycle of the output

subcarriers.

For NDLRB 25, the block returns 12×25=300 resource grid samples. The block

indicates the location of these output samples with the

validOut signal set to 1 (true). The

validOut signal is 0 (false) at the

center of the output samples, to exclude the DC carrier.

This waveform shows the output when you set the Input data sample

rate parameter to Use maximum input data sample

rate and select an NDLRB of 25 with normal CP.

This waveform shows the output of the block when you set the Input data

sample rate parameter to Match input data sample rate to

NDLRB and select an NDLRB of 25 with normal CP. The block repeats

four times at the input of FFT for computing 2048-point FFT. The actual FFT samples

are taken for every one in four samples at the output of FFT. The block chooses the

center (12×25 = 300) resource grid elements and outputs them along with valid

signal.

The performance of the synthesized HDL code varies with your target and synthesis

options. The input data type used for generating HDL code is

fixdt(1,16,14).

This table shows the resource and performance data synthesis results when using the block with default configuration. The generated HDL targeted to an AMD® Zynq® XC7Z045I-FFG900-2L FPGA. The design achieves a clock frequency of 280 MHz.

| Resource | Number Used |

|---|---|

| LUTs | 6072 |

| Registers | 8291 |

| DSPs | 16 |

| Block RAM | 23 |

| F7 Muxes | 0 |

| F8 Muxes | 0 |

| RAMB36/FIFO | 6 |

| RAMB18 | 18 |

References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

[2] Sesia, S., I. Toufik, and M. Baker, eds. LTE - The UMTS Long Term Evolution : From Theory to Practice. Hoboken, NJ: John Wiley & Sons Ltd., 2009.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2018a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Sélectionner un site web

Choisissez un site web pour accéder au contenu traduit dans votre langue (lorsqu'il est disponible) et voir les événements et les offres locales. D’après votre position, nous vous recommandons de sélectionner la région suivante : .

Vous pouvez également sélectionner un site web dans la liste suivante :

Comment optimiser les performances du site

Pour optimiser les performances du site, sélectionnez la région Chine (en chinois ou en anglais). Les sites de MathWorks pour les autres pays ne sont pas optimisés pour les visites provenant de votre région.

Amériques

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)