Cette page a été traduite automatiquement.

Merci de bien vouloir compléter un sondage de 1 minute concernant la qualité de cette traduction.

L'ETRI accélère les émulations radar en exécutant des algorithmes sur des FPGA NI

Un nouveau workflow réduit de 50 % le temps et les efforts nécessaires à l’implémentation de code HDL

« Il est particulièrement utile que la majeure partie du code de l’algorithme principal puisse être utilisé telle quelle, sans aucun travail supplémentaire, en utilisant des blocs de fonctions MATLAB. Même sans aucune expertise du langage HDL, il a été facile de convertir l'algorithme en code HDL à l'aide de HDL Coder. »

Principaux résultats

- Le temps et les efforts nécessaires à l’implémentation du code HDL ont été réduits de 50 % par rapport aux workflows traditionnels impliquant du code manuscrit ou d'autres méthodes de design.

- L'effort de vérification a été réduit de 50 % en utilisant la cosimulation pour comparer le comportement de l'algorithme et du code HDL généré.

- Le traitement du signal en temps réel du FPGA cible a permis la vérification comportementale et les tests de performance au niveau système.

L'Institut de recherche en électronique et télécommunications (ETRI) est un leader dans le domaine des technologies de l'information et des communications en Corée. Sa division de recherche radio a utilisé MATLAB® pour développer un module de traitement de signaux d'émission/réception en temps réel, pour un banc d'essai radar basse consommation. Cependant, son exécution sur un processeur utilisant un environnement de programmation graphique tiers ne répondait pas aux exigences du projet. En particulier, les algorithmes de traitement parallèle, tels que les banques de filtres adaptés pour réduire les interférences de signaux, nécessitaient une exécution en temps réel, et les récepteurs de signaux orthogonaux devaient être implémentés dans une structure pipelinée.

L’équipe ETRI a donc jugé nécessaire de migrer vers un FPGA NI™ pour atteindre ses objectifs. Convertir directement l’algorithme MATLAB en HDL était hors de question, car le code aurait dû être modifié manuellement après chaque modification de l’algorithme. De plus, le débuggage était complexe car la structure de l’algorithme ne se reflétait pas de manière identique dans le code HDL.

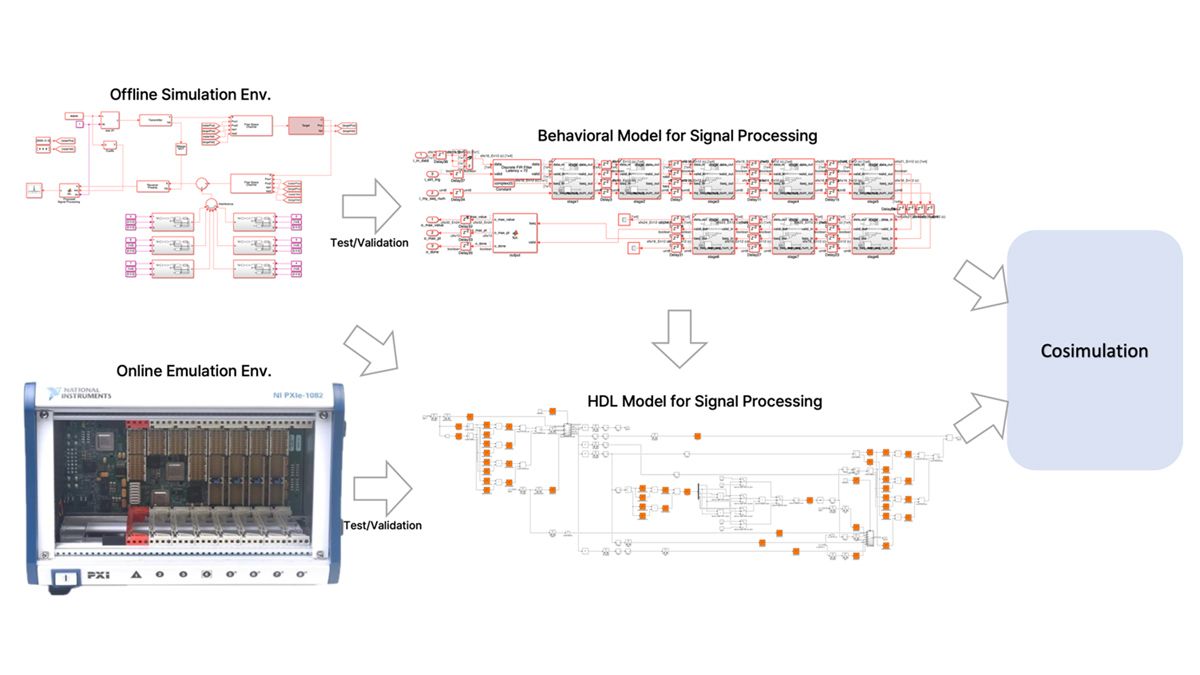

Dans le but de continuer à exploiter leur propriété intellectuelle, ainsi que les exemples et le support fournis par MathWorks, l'équipe a d'abord converti l'algorithme vers Simulink®, puis généré le code HDL à l'aide de HDL Coder™. Les compromis entre les différentes options de design pour l’implémentation, l’architecture matérielle et les types de données à virgule fixe ont ainsi été facilement évalués. Les concepteurs de l’algorithme et du matériel ont pu collaborer grâce à la cosimulation, ce qui a permis de réduire les itérations entre les ingénieurs et de minimiser les répétitions et les erreurs humaines.

Au-delà de cela, ce workflow a offert aux ingénieurs d'ETRI un processus de design et de vérification adapté où le modèle Simulink et le code HDL avaient exactement la même structure. L’utilisation de HDL Verifier™ a rendu possible une vérification comportementale et des tests de performances en temps réel au niveau système. Grâce à l’automatisation, ce workflow a permis d’économiser environ 50 % du temps et des efforts nécessaires à l’implémentation du code HDL et à la vérification comportementale en temps réel. Les projets futurs, tels que ceux impliquant des algorithmes basés sur le Machine Learning, devraient également utiliser la génération de code avec HDL Coder.

Produits utilisés