FPGA Data Capture

Capture data from live FPGA into MATLAB workspace interactively

Description

Add-On Required: This feature requires one of these add-ons.

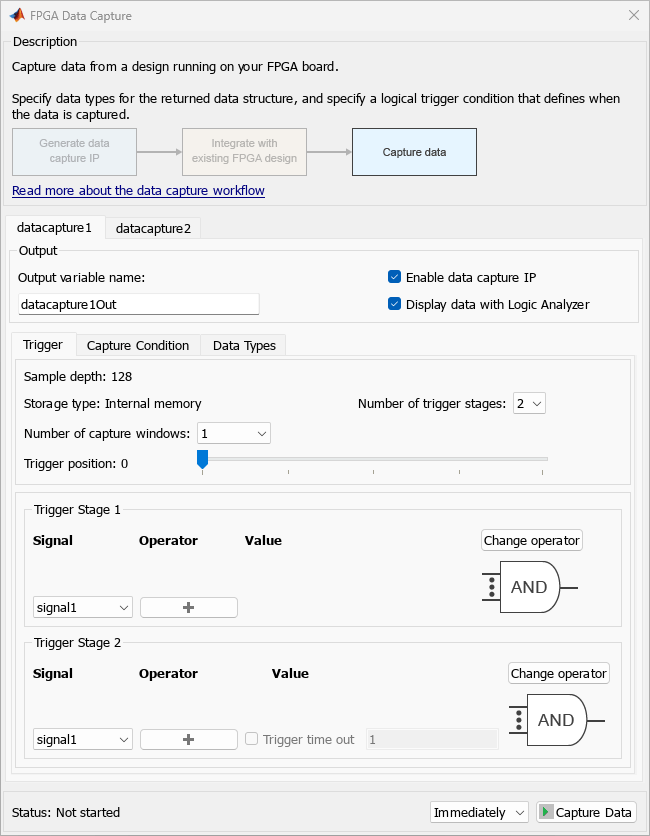

The FPGA Data Capture tool captures data from a design running on an FPGA and returns it to the MATLAB® workspace. You can configure the data types of the returned values, specify the number of capture windows and number of trigger stages, set up a trigger condition to control when the data is captured, and set up a capture condition to control which data to capture.

Before using this tool, you must have generated the customized data capture components using the FPGA Data Capture Component Generator tool. You must also integrate the generated IP core into your project and deploy it to the FPGA. The tool communicates with the FPGA over a JTAG, Ethernet, or USB Ethernet cable. Make sure that the required cable is connected between the board and the host computer.

The tool is a wrapper over your generated hdlverifier.FPGADataReader

System object™. The FPGA Data Capture tool

defines the variable, fpgadc_obj in the workspace. If this variable

already exists, the tool opens using the existing object, and saves modifications to

that object.

For a workflow overview, see Data Capture Workflow.

For an AMD® device over a JTAG connection, you can observe signals operating at different clock rates by using multiple data capture IPs. For more information about how to generate and integrate multiple data capture IPs into your FPGA design, see Capture Asynchronous Data.

Open the FPGA Data Capture

MATLAB command prompt: Enter

launchDataCaptureApp. This function opens the FPGA Data Capture tool for a single data capture IP.The

launchDataCaptureAppfunction is a generated script in thedestinationFolderdestinationFolder\generatedIPNamedestinationFoldergeneratedIPNameMATLAB command prompt: Enter

launchMultipleDataCaptureApp. This function opens the FPGA Data Capture tool for multiple data capture IPs.The

launchMultipleDataCaptureAppfunction is a generated script in thedestinationFolderdestinationFolder

Examples

Parameters

Version History

Introduced in R2017a