Capture Conditions

What Is Capture Condition?

A capture condition is a logical statement that controls which data to capture from the FPGA. Use a capture condition when you want to:

Capture only the valid data to debug custom designs with FPGA data capture.

Filter the data to capture based on trigger conditions.

Optimize the use of an FPGA data capture buffer.

Efficiently analyze the captured data when you have only a few captured samples of interest.

A capture condition is composed of value comparison tests on one or more FPGA signals. For example:

counter == 100

All capture comparisons are synchronous. When you specify an edge condition for a Boolean signal, the IP core compares the current sampled value with the sampled value from the previous clock cycle.

fifo_full == 'Rising edge'

The capture condition is met when all terms of the condition are true on the same clock cycle. You can use only a single value comparison per signal.

receiver_state == 3 OR message_detected == 'High'

fifo_cnt == 0 AND fifo_pop == 'High'

You can use only a single type of logical operator in the capture condition. You cannot mix

AND and OR conditions.

fifo_empty == 'Rising edge' OR fifo_full == 'Rising edge' OR memctrl_state == 2

receiver_state == 3 AND message_addr == 148 AND pkt_type == 5

You can use multiple comparison operators in the capture condition.

fifo_empty == 'Rising edge' OR fifo_full != 'LOW' OR memctrl_state == 2

receiver_state == 3 AND message_addr > 148 AND pkt_type >= 5

You can use X or x (don't-care value) in the capture

condition. While comparing, the capture condition ignores the place values with

X. When the capture condition is 0b1X1, the possible

trigger condition values are 0b101 or 0b111.

receiver_state == 3 AND message_addr == 148 AND pkt_type == 0b1X1

Configure Capture Condition

At generation time, specify which signals you want to be available for use in the capture condition. You can use a signal containing only a trigger or both a trigger and captured data. You can modify the capture condition at capture time using any signals you specify as triggers. Also, at generation time, you can include capture condition logic to use the capture condition. The data capture IP core on the FPGA receives the capture definition from MATLAB® and configures on-chip muxes to detect the capture event.

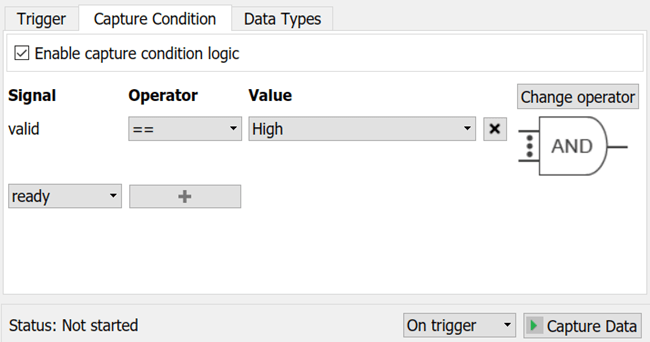

When you use the FPGA Data Capture tool or the FPGA Data Reader block, on the Capture Condition tab, select the Enable capture condition logic parameter and then set the capture condition. Each line in the table is the value comparison for one signal. To combine the signal values, use the capture condition combination operator. To show a signal on this tab, you must specify the signal as a trigger at generation time.

For an hdlverifier.FPGADataReader

System object™, enable capture condition logic using the EnableCaptureCtrl property. Then

configure the capture condition using the setCaptureCondition,

setCaptureConditionComparisonOperator, and setCaptureConditionCombinationOperator object functions. To check your

configuration, call the displayCaptureCondition object function.

Differences Between Triggers and Capture Conditions

The trigger condition controls when to capture data from the FPGA. Once the trigger condition is satisfied, the data capture IP core captures data from that trigger event. The capture condition controls which data to capture. The data capture IP core evaluates the capture condition at each clock cycle and captures only the data that satisfies the capture condition.

FPGA data capture operates in two modes: immediate mode and trigger mode. The data capture IP core captures data from the FPGA without checking for the trigger condition in immediate mode and based on a trigger condition in trigger mode. You can provide a capture condition in both modes.

Filter the data to capture using a capture condition. In immediate mode, use a capture condition to capture data only when a certain condition is met. In trigger mode, use a capture condition to capture data only when a certain condition is met after satisfying the trigger condition.

| Data Capture Mode | Trigger Condition Only | Capture Condition Only | Both Trigger and Capture Conditions |

|---|---|---|---|

| Immediate | Ignores all trigger conditions Captures data immediately at each clock cycle | Captures data only when the capture condition is true | Ignores all trigger conditions Captures data only when the capture condition is true |

| Trigger | Waits until the trigger condition is true, then captures data | Not supported, use immediate mode instead | Waits until the trigger condition is true, then captures data only when the capture condition is true |