uvmfbuild

Description

Add-On Required: This feature requires the ASIC Testbench for HDL Verifier add-on.

uvmfbuild(Predictor=

generates UVM sequence and predictor components and a YAML file that is UVM framework (UVMF)

compliant from a Simulink® model.predictorSubsystem,Sequence=sequenceSubsystem)

Use the generated YAML file and UVM components with Siemens® UVMF tools for testbench generation and RTL validation.

Examples

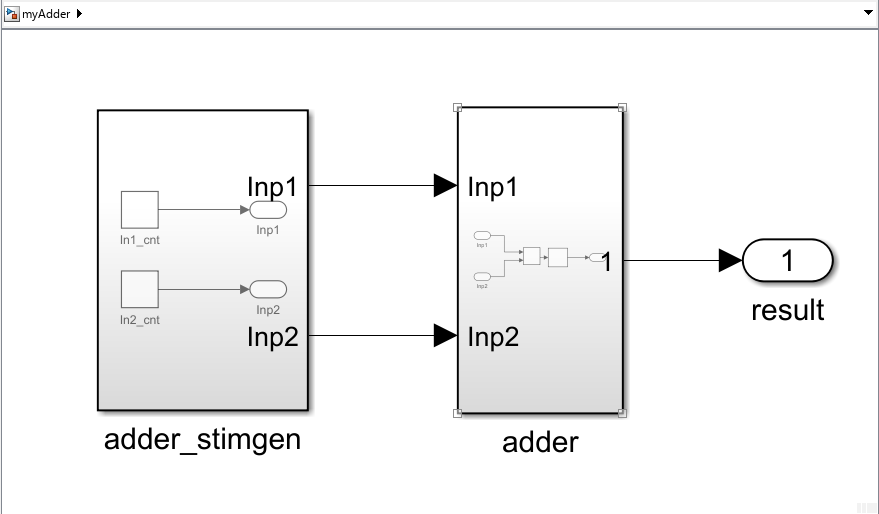

Generate the following artifacts from the myAdder model:

A UVM sequence component for the adder_stimgen subsystem

A UVM predictor component for the adder subsystem

A YAML file for UVM Framework

open_system("myAdder"); uvmfbuild(Predictor='myAdder/adder',Sequence='myAdder/adder_stimgen');

### Generating DPI components for all the specified subsystems ### Searching for referenced models in model 'adder'. ### Total of 1 models to build. ### Starting build procedure for model: adder ### Generating code and artifacts to 'Model specific' folder structure ### Generating code into build folder: /tmp/Bdoc26a_3233028_208344/tp82218b69/hdlverifier-ex92377061/uvmfbuild/adder_build ### Invoking Target Language Compiler on adder.rtw ### Using System Target File: /mathworks/devel/bat/filer/batfs2566-0/Bdoc26a.3233028/build/runnable/matlab/toolbox/hdlverifier/dpigenerator/rtw/systemverilog_dpi_grt.tlc ### Loading TLC function libraries ........ ### Initial pass through model to cache user defined code ### Caching model source code ........ ### Generating TLC interface API. ... ### Writing source file adder_capi.c . ### Writing header file adder_capi.h ............................... ### Writing header file adder_types.h . ### Writing header file adder.h ### Writing header file rtwtypes.h ### Writing header file builtin_typeid_types.h ### Writing header file multiword_types.h ### Writing source file adder.c . ### Writing header file adder_private.h ### Writing header file rtmodel.h ### TLC code generation complete (took 1.539s). ### Starting SystemVerilog DPI Component Generation ### Saving binary information cache. ### Generating DPI H Wrapper adder_dpi.h ### Generating DPI-C Wrapper adder_dpi.c ### Generating file adder_dpi_pkg.sv ### Generating file uvmf_component.yaml ### Generating makefiles for: adder_dpi ### Using toolchain: GNU gcc/g++ | gmake (64-bit Linux) ### Creating '/tmp/Bdoc26a_3233028_208344/tp82218b69/hdlverifier-ex92377061/uvmfbuild/adder_build/adder.mk' ... ### Successful completion of build procedure for model: adder Build Summary Top model targets: Model Build Reason Status Build Duration =========================================================================================== adder Information cache folder or artifacts were missing. Code generated. 0h 0m 5.1458s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 5.4332s ### Searching for referenced models in model 'adder_stimgen'. ### Total of 1 models to build. ### Starting build procedure for model: adder_stimgen ### Generating code and artifacts to 'Model specific' folder structure ### Generating code into build folder: /tmp/Bdoc26a_3233028_208344/tp82218b69/hdlverifier-ex92377061/uvmfbuild/adder_stimgen_build ### Invoking Target Language Compiler on adder_stimgen.rtw ### Using System Target File: /mathworks/devel/bat/filer/batfs2566-0/Bdoc26a.3233028/build/runnable/matlab/toolbox/hdlverifier/dpigenerator/rtw/systemverilog_dpi_grt.tlc ### Loading TLC function libraries ........ ### Initial pass through model to cache user defined code ### Caching model source code ......... ### Generating TLC interface API. ..... ### Writing source file adder_stimgen_capi.c .. ### Writing header file adder_stimgen_capi.h ............................... ### Writing header file adder_stimgen_types.h ### Writing header file adder_stimgen.h ### Writing header file rtwtypes.h ### Writing header file builtin_typeid_types.h ### Writing header file multiword_types.h . ### Writing source file adder_stimgen.c ### Writing header file adder_stimgen_private.h ### Writing header file rtmodel.h ### TLC code generation complete (took 1.608s). .### Starting SystemVerilog DPI Component Generation ### Saving binary information cache. ### Generating DPI H Wrapper adder_stimgen_dpi.h ### Generating DPI-C Wrapper adder_stimgen_dpi.c ### Generating file adder_stimgen_dpi_pkg.sv ### Generating file uvmf_component.yaml ### Generating makefiles for: adder_stimgen_dpi ### Using toolchain: GNU gcc/g++ | gmake (64-bit Linux) ### Creating '/tmp/Bdoc26a_3233028_208344/tp82218b69/hdlverifier-ex92377061/uvmfbuild/adder_stimgen_build/adder_stimgen.mk' ... ### Successful completion of build procedure for model: adder_stimgen Build Summary Top model targets: Model Build Reason Status Build Duration =================================================================================================== adder_stimgen Information cache folder or artifacts were missing. Code generated. 0h 0m 4.4573s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 4.6363s ### Generating file uvmftb.yaml ### Generating UVM Framework test bench YAML file uvmftb.yaml

You can now use these files with Siemens® UVM Framework tools to generate a full UVM testbench.

Input Arguments

Name of the predictor subsystem, specified as a string.

Name of the sequence subsystem, specified as a string.

Version History

Introduced in R2025a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Sélectionner un site web

Choisissez un site web pour accéder au contenu traduit dans votre langue (lorsqu'il est disponible) et voir les événements et les offres locales. D’après votre position, nous vous recommandons de sélectionner la région suivante : .

Vous pouvez également sélectionner un site web dans la liste suivante :

Comment optimiser les performances du site

Pour optimiser les performances du site, sélectionnez la région Chine (en chinois ou en anglais). Les sites de MathWorks pour les autres pays ne sont pas optimisés pour les visites provenant de votre région.

Amériques

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)