Use Harness Model for Test Simulations

Harness Model Generation

A harness model provides an isolated environment to test design changes. You can create a harness model during Simulink® Design Verifier™ analysis or after the analysis.

The contents of the harness model depend on the value of the Mode parameter, set in the Configuration Parameters dialog box on the Design Verifier pane:

Design error detection— The harness model contains the test cases that result in errors during simulation.Test generation— The harness model contains the test cases that achieve test objectives.Property proving— The harness model contains counterexamples that falsify the proof objectives.

By default, the Generate separate harness model after analysis parameter is disabled. A harness model is created following a Simulink Design Verifier analysis only if the analysis has produced at least one test case or counterexample.

Note

The Simulink Design Verifier software generates a harness model only when the top-level model that you are analyzing contains an Inport block.

Create a Harness Model

To create a harness model before or after the analysis, use these methods:

Before the analysis, in the Configuration Parameters dialog box, on the Design Verifier > Results pane, select Generate separate harness model after analysis.

After the analysis, in the Simulink Design Verifier Results Summary window, select Create harness model.

Contents of a Harness Model

Simulink Design Verifier software creates a harness model that contains these items:

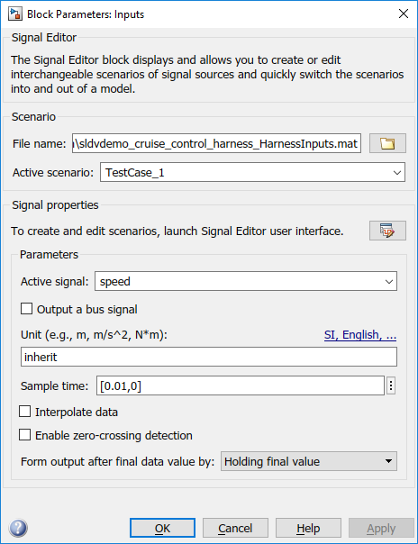

Inputs — The Inputs block is a Signal Editor block. This block contains scenarios that are comprised of the test cases or counterexamples that Simulink Design Verifier generates. The Signal Editor block contains signals only for input signals that are used in the model. If an input signal has no effect on the output of the model, that signal is not included in the Signal Editor block.

After Simulink Design Verifier generates harness model, the input MAT file for the Signal Editor block is saved at the default location

<current_folder>\sldv_output\<model_name>\<model_name>_harness_HarnessInputs.mat.

To open the Signal Editor dialog box and view the scenarios of signal sources, double-click the Inputs block. The Active scenario lists the test cases or counterexamples. To create and edit scenarios, launch the Signal Editor user interface. For more information, see Create and Edit Signal Data.

If you select the

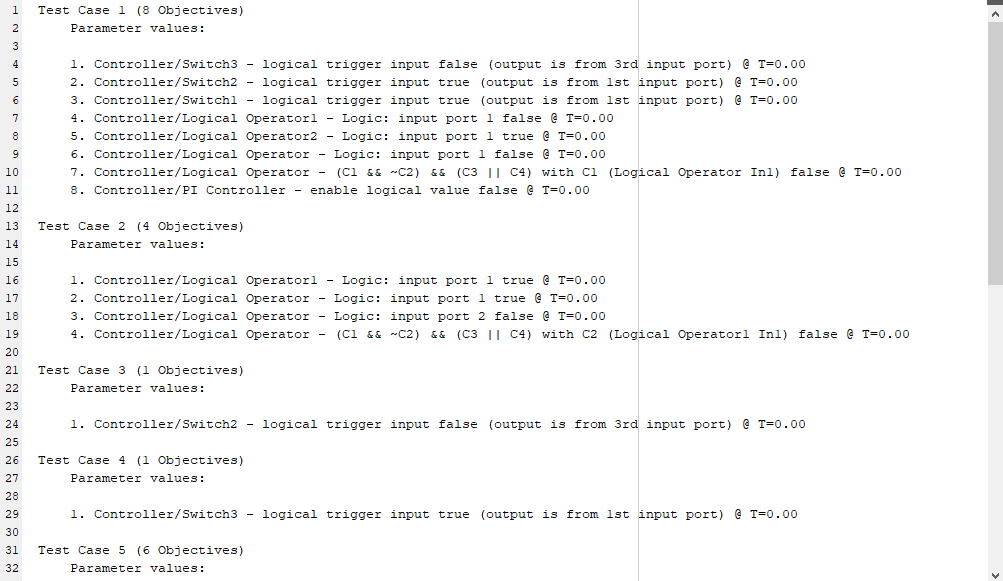

LongTestcasesoption of the Test suite optimization parameter, the analysis creates fewer, longer test cases. For example, if you select theLongTestcasesoption for thesldvdemo_cruise_controlmodel, the analysis produces one long test case instead of nine shorter test cases.Size-Type — This Subsystem block transmits signals from the Inputs block to the Test Unit block. It verifies that the size and data type of the signals are consistent with the Test Unit block.

Test Unit — This Model block references the original model that Simulink Design Verifier analyzed.

If you do not select the Reference input model in generated harness on the Design Verifier > Results pane in the Configuration Parameters dialog box, the Test Unit created is a Subsystem block.

If the Test Unit in the harness model is a subsystem, the values of the parameters on the Optimization and Math and Data Types panes might impact the coverage results.

Test Case Explanation — This DocBlock block documents the test cases or counterexamples that Simulink Design Verifier generates. To view the description of each test case or counterexample, double-click the Test Case Explanation block. The block lists either the test objectives that each test case achieves or the proof objectives that each counterexample falsifies.

Configuration of the Harness Model

Simulink Design Verifier generates the harness model with these settings.

The harness model start time is always

0. If the original model uses a nonzero start time, the software ignores the start time and uses0for the simulation start time for test cases and counterexamples.The harness model stop time always equals the stop time of the longest test case in the Inputs block.

By default, the software enables coverage analysis and generates a coverage report for the harness models that contain test cases. The coverage reporting is enabled with default options. You can customize these settings by using the Coverage Pane (Simulink Coverage).

By default, if you select Ignore objective based on filter and provide a coverage filter file for the Test Unit, the coverage filter file applies to the harness model. For more information, see Coverage data.

For models that use the complex type Inport block, a Signal Editor block is used as the harness source regardless of the Harness source that you specify.

Simulate the Harness Model

The harness model enables you to simulate a copy of your original model by using the test cases or counterexamples that Simulink Design Verifier generates. Using the harness model, you can simulate:

A counterexample.

A single test case, for which the Simulink Coverage™ software collects and displays model coverage information.

All the test cases, for which the Simulink Coverage software collects and displays cumulative model coverage information.

Note

If you analyze a model that is simulated with sample time warnings, when you simulate the harness model, the warnings might be reported as errors, causing the simulation to fail.

Simulate Harness Model by Using the Signal Editor Inputs Block

To simulate a single test case or counterexample:

In the harness model, double-click the Inputs block.

In the Signal Editor dialog box, select the Active scenario with a particular test case or counterexample and click OK.

In the Simulink editor, click the Run button.

The Simulink software simulates the harness model by using the scenario of signal sources associated with the selected test case or counterexample. When simulating a test case, the Simulink Coverage software collects model coverage information and displays a coverage report.

To simulate all the test cases and measure their combined model coverage, use cvsim (Simulink Coverage)

or parsim command. For example, see Simulate Harness Model with

Signal Editor Inputs Block.

See Also

Creating and Executing Test Cases | Perform Analysis on Model