Using ARM Cortex-M Coprocessor

The ARM® Cortex®-M processor provides higher-level external connectivity, such as network communication. Using the ARM Cortex-M processor for asynchronous communication and supervisory tasks frees up the other CPUs to perform time-critical tasks concurrently. The ARM Cortex-M processor supports several higher-level communication APIs, such as UDP and TCP, that are not available on the C2000™ processors.

Configure C2000 Model with ARM Cortex-M Processor

A C2000 processor with ARM Cortex-M processor consists of a Task Manager (SoC Blockset) block and reference Model block containing the tasks for execution on each processor in the system. This model contains sample models of the C2000 processor and ARM Cortex-M processor, each with a timer-driven task.

Configure C2000 Top-Level Model

Open a new Simulink® model. Save the model as

tif2838xD_top.slx.Configure the

tif2838xD_top.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

None.Click Finish.

Configure C2000 Processor Model

Open a new Simulink model. Save the model as

tif2838xD_c28xCPU1.slx.Configure the

tif2838xD_c28xCPU1.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

c28xCPU1.Click Finish.

Add the event- and timer-driven tasks to the C2000 processor model.

In the

tif2838xD_top.slxmodel, add Task Manager (SoC Blockset) and Model blocks.Assign the

tif2838xD_c28xCPU1.slxmodel to the Model block and then connect the tasks to the Task Manager block.

Configure ARM Cortex-M Processor Model

Open a new Simulink model. Save the model as

tif2838xD_ARMCPU3.slx.Configure the

tif2838xD_ARMCPU3.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

CortexM4.Click Finish.

Add event- or timer-driven tasks to the ARM Cortex-M model.

In the

tif2838xD_top.slxmodel, add Task Manager (SoC Blockset) and Model blocks.Assign the

tif2838xD_ARMCPU3.slxmodel to the Model block and then connect the tasks to the Task Manager block.

Configure C2000 and ARM Cortex-M Processor Model

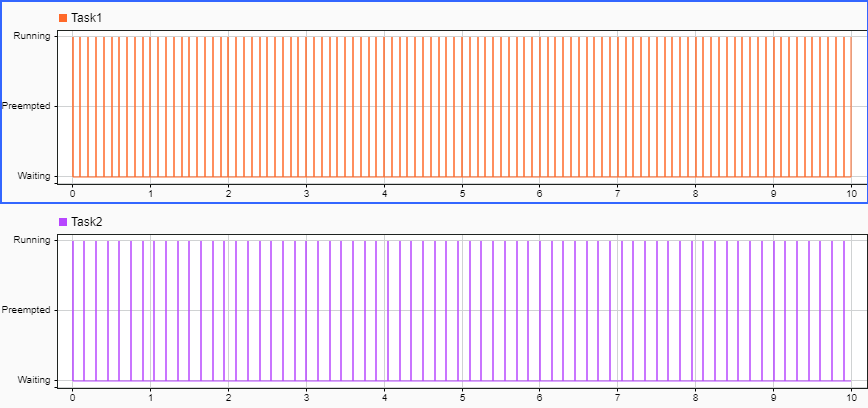

This example shows how to create a C2000 model that contains the C2000 processor and the ARM Cortex-M connectivity manager (CM) processor. The C2000 and ARM Cortex-M processors contain time-varying tasks that execute at rates of 0.1 and 0.15 seconds, respectively. Open the model.

open_system("c2000_armcortexm_top_level_model.slx")

Run the model and inspect the task execution in the Simulation Data Inspector. As separate processors, the tasks run without interfering with each other's execution.

Connection Between C2000 and ARM Cortex-M Processors

The C2000 processors can connect to the ARM

Cortex-M processor using the Interprocess Data

Read (SoC Blockset), Interprocess Data

Channel (SoC Blockset), and Interprocess Data

Write (SoC Blockset) block triplet. The block triplet simulates the exchange of data

between the C2000 processor and the ARM

Cortex-M processor. When the model generates code, custom flags in the

CPU module with data being

transferred through shared memory, such as the

x-CM IPCS RAM, replaces the block triplet for

the specified C2000 processor.n

Data Exchange Between CPU and ARM Processors

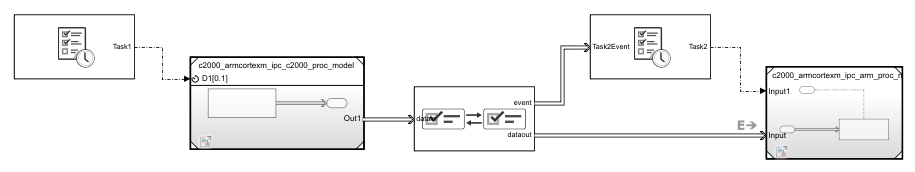

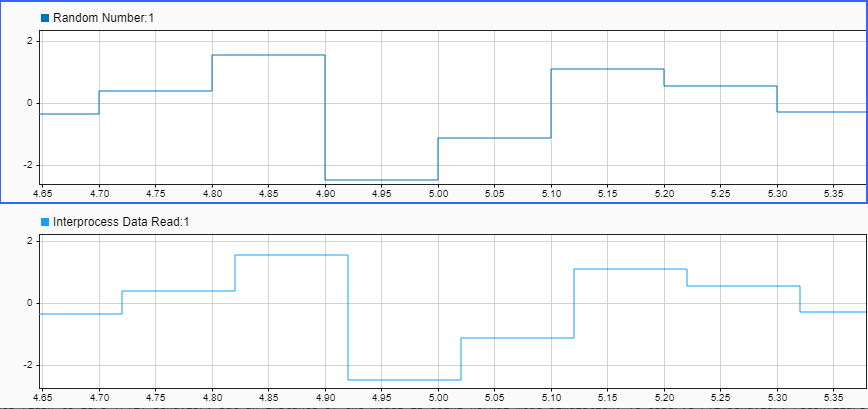

This example shows how to transfer data between the C2000 processor and the ARM Cortex-M processor. The C2000 processor and ARM coprocessor can share data with the Interprocess Data Channel (SoC Blockset), Interprocess Data Read (SoC Blockset), and Interprocess Data Write (SoC Blockset) blocks. This model shows a timer-driven task on the C2000 processor that transmits a random number over the Interprocessor Data Channel block to the ARM processor. When the ARM processor receives the data, the task triggers and reads the data packet. Open the model.

open_system("c2000_armcortexm_ipc_top_level_model.slx");

This figure shows the Simulation Data Inspector view of the data and tasks in the applications. The delay between the CPU and CLA measurements is due to the CPU completing the transmission before the start of the CLA task.

See Also

Task Manager | Interprocess Data Read | Interprocess Data Channel | Interprocess Data Write | UDP Read (SoC Blockset) | UDP Write (SoC Blockset)