expand all

The OFDM Equalizer block supports ZF and MMSE algorithms for channel

equalization in the frequency domain. The block stores the estimated channel information to

equalize the OFDM symbols and generates the equalized output using these algorithms.

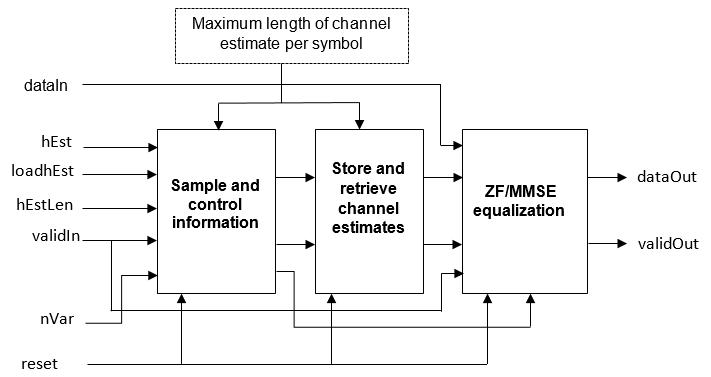

The OFDM Equalizer block operation sequence is implemented using these

subsystem blocks: Sample and control information, Store and retrieve channel estimates, and

ZF/MMSE equalization. This figure shows these blocks.

The Sample and control information block samples and validates the

hEstLen input based on the loadhEst input signal,

validates the hEst and nVar inputs based on the

validIn input signal, and outputs the sampled hEstOut

output, nVarOut output, and the control information signals

that are used in storing and retrieving channel information. The Store and retrieve

channel estimates block stores and retrieves the channel using RAM and switches. The

ZF/MMSE Equalization block performs ZF or MMSE equalization using these

equations. The nVar input port is available when you set the

Equalization method parameter to

MMSE.

ZF Algorithm:

MMSE Algorithm:

In these equations,

dataIn is the demodulated output provided as an input to the

block

hEst is the estimated channel

hEst* is the Hermitian of the estimated

channel

dataOut is the equalized output

nVar is the noise variance

p is equal to 0, 1, …. NSPS, where

NSPS is the number of subcarriers per symbol.

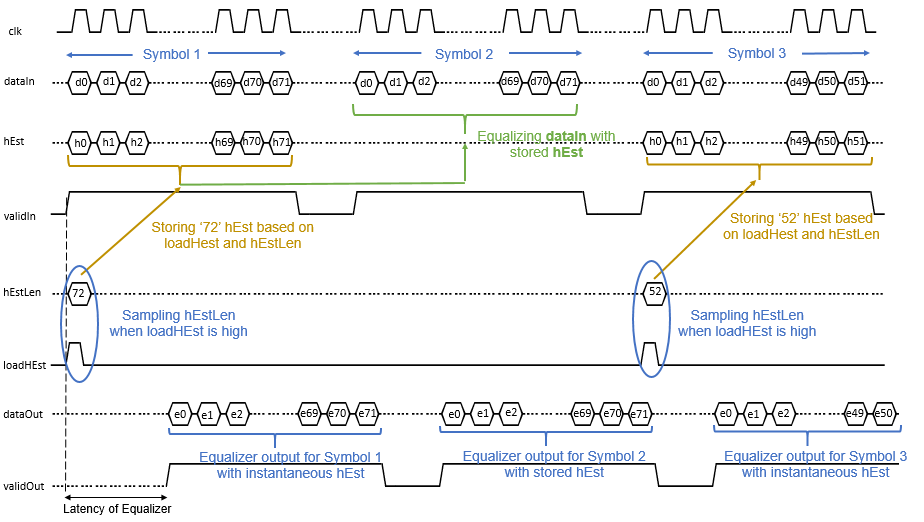

This figure shows a sample block operation when you set the Equalization

method parameter to ZF.

In this figure, you can see three symbols (Symbol 1, Symbol 2, and Symbol 3) are input to

the dataIn port. When the validIn input is

1 (high) and the loadHest input is

1 (high), the block samples the hEstlLen input

value, which is 72 in this example. Based on the

hEstlLen value, for Symbol 1, the block provides the equalized output

for the instantaneous hEst input values. When the

loadHest value changes to 0 (low), the block stores

the hEst values and provides the equalized output for Symbol 2 based on

the stored hEst values. The hEstLen value remains

the same until the loadHest changes to 0 (low).

Similarly, for Symbol 3, the block provides the equalized output for the instantaneous

hEst values based on the hEstlLen value, which is

52 in this example.

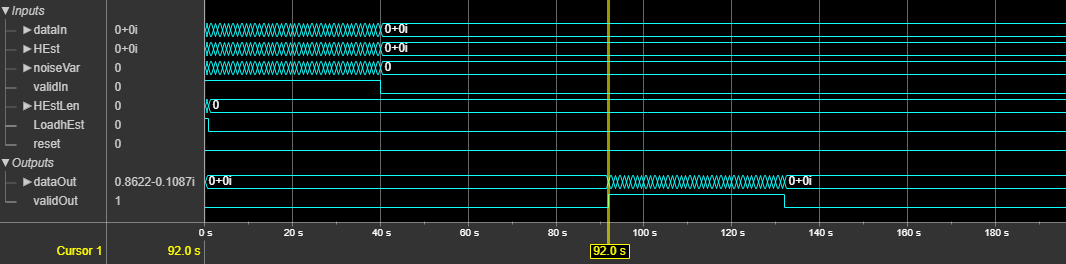

This figure shows a sample output of the OFDM Equalizer block when you

set the Equalization method parameter to MMSE and

the Maximum length of channel estimate per symbol parameter to

52. The latency of the block is 92 clock cycles.

The performance of the synthesized HDL code varies with your target and synthesis

options.

This table shows the resource and performance data synthesis results of the block when

you set the Equalization method parameter to MMSE,

the Maximum length of channel estimate per symbol parameter to

52, and the hEstLen port to 20.

The input data is of data type fixdt(1,28,16). The generated HDL is

targeted to the AMD®

Zynq®- 7000 ZC706 evaluation board. The design achieves a clock frequency of 244.6

MHz.

| Resource | Number Used |

|---|

| Slice LUTs | 7380 |

| Slice Registers | 8063 |

| DSPs | 24 |

| Block RAMs | 0 |