La traduction de cette page n'est pas à jour. Cliquez ici pour voir la dernière version en anglais.

Démarrer avec Simulink Design Verifier

Simulink® Design Verifier™ utilise des méthodes formelles pour identifier les erreurs de design cachées dans les modèles. Il détecte les blocs du modèle qui entraînent des problèmes de dépassement d'entier, de logique morte, de violation d'accès aux tableaux et de division par zéro. Il peut vérifier de manière formelle que le design répond aux exigences fonctionnelles. Pour chaque erreur de design et chaque exigence non respectée, il génère un cas de test de simulation pour le débuggage.

Simulink Design Verifier génère des cas de test pour la couverture du modèle, ainsi que des objectifs personnalisés afin d'étendre les cas de tests existants basés sur les exigences. Ces cas de test permettent à votre modèle de remplir les objectifs de condition, de décision, de condition/décision modifiée (MCDC) et les objectifs de couverture personnalisés. En plus des objectifs de couverture, vous pouvez spécifier des objectifs de test personnalisés pour générer automatiquement des cas de test basés sur les exigences.

Le support des normes industrielles est assuré via l’IEC Certification Kit (pour les normes CEI 61508 et ISO 26262) et DO Qualification Kit (pour DO-178).

Tutoriels

- Utiliser Simulink Design Verifier pour la vérification systématique d’un modèle

Découvrir les fondamentaux d’une analyse Simulink Design Verifier.

- ÉTAPE 1: Préparer le modèle à l’analyse de génération de tests

- ÉTAPE 2: Configurer les paramètres du modèle et exécuter une analyse

- ÉTAPE 3: Examiner les résultats de l’analyse de génération de tests

- ÉTAPE 1: Préparer le modèle à l’analyse de détection des erreurs de design

- ÉTAPE 2: Détecter les erreurs de design courantes

- ÉTAPE 3: Exécuter l’analyse de détection des erreurs de design

- ÉTAPE 4: Examiner les résultats de l’analyse de détection des erreurs de design

- ÉTAPE 5: Corriger les erreurs de design d’un modèle

Générer des cas de test pour un modèle

Préparer un modèle, configurer ses paramètres et examiner les résultats de l’analyse de la génération du test.

Détecter les erreurs de design dans un modèle

Configurer les réglages du modèle, détecter les erreurs de design et examiner les résultats.

Sélection d՚exemples

Vidéos

Qu’est-ce que Simulink Design Verifier ?

Introduction à Simulink Design Verifier.

Comment utiliser Simulink Design Verifier pour détecter automatiquement les erreurs de design dans vos modèles Simulink

Utiliser Simulink Design Verifier pour trouver des erreurs dans un design, et comment les erreurs, lorsqu’elles sont détectées, peuvent être débuggées à l’aide des fonctionnalités de visualisation de Simulink Design Verifier.

DO-178C Workflow pour la génération automatique de vecteurs de test

Utiliser Simulink Design Verifier pour générer automatiquement des vecteurs de test afin d’analyser la couverture manquante du modèle, collectée par Simulink Coverage, pour se conformer à la norme DO-178C et à ses suppléments.

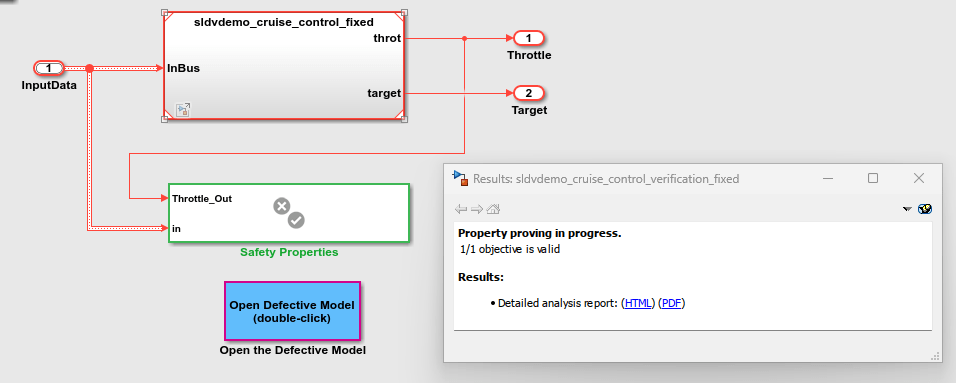

Comment débugger un contre-exemple de preuve de propriétés

La preuve de propriété avec Simulink Design Verifier™ est une technique d’analyse statique qui utilise des méthodes formelles pour prouver qu’une propriété donnée sera toujours valide. Cette technique peut vous aider à vérifier formellement que les exigences spécifiques implémentées dans votre design seront toujours respectées.

workflow de test basé sur les exigences

Explique comment créer un test au moyen d’une séquence de test, définir une évaluation formelle, lier les cas de test aux exigences, exécuter des suites de test et analyser la couverture de test manquante du modèle.