SPICE NJFET

SPICE-compatible N-Channel JFET

Libraries:

Simscape /

Electrical /

Additional Components /

SPICE Semiconductors

Description

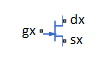

The SPICE NJFET block represents a SPICE-compatible N-channel junction field-effect transistor (NJFET). If the voltage applied to the gate port, gx, is less than the voltage applied to the source port, sx, the current between the source port and drain port, dx, is reduced.

SPICE, or Simulation Program with Integrated Circuit Emphasis,

is a simulation tool for electronic circuits. You can convert some SPICE subcircuits into

equivalent Simscape™

Electrical™ models using the Environment Parameters block and

SPICE-compatible blocks from the Additional Components library. For more

information, see subcircuit2ssc.

Equations

Variables for the SPICE NJFET block equations include:

Variables that you define by specifying parameters for the SPICE NJFET block. The visibility of some of the parameters depends on the value that you set for other parameters. For more information, see Parameters.

Geometry-adjusted variables, which depend on several values that you specify using parameters for the SPICE NJFET block. For more information, see Geometry-Adjusted Variables.

Temperature, T, which is

300.15Kby default. You can use a different value by specifying parameters for the SPICE NJFET block or by specifying parameters for both the SPICE NJFET block and an Environment Parameters block. For more information, see Transistor Temperature.Temperature-dependent variables. For more information, see Temperature Dependence.

Minimal conductance, GMIN, which is

1e-121/Ohmby default. You can use a different value by specifying a parameter for an Environment Parameters block. For more information, see Minimal Conduction.

Several variables in the equations for the N-channel junction field-effect transistor model consider the geometry of the device that the block represents. These geometry-adjusted variables depend on variables that you define by specifying SPICE NJFET block parameters. The geometry-adjusted variables depend on these variables:

AREA — Area of the device

SCALE — Number of parallel connected devices

The associated unadjusted variable

The table includes the geometry-adjusted variables and the defining equations.

| Variable | Description | Equation |

|---|---|---|

| BETAd | Geometry-adjusted transconductance |

|

| CGDd | Geometry-adjusted zero-bias gate-drain capacitance |

|

| CGSd | Geometry-adjusted zero-bias gate-source capacitance |

|

| ISd | Geometry-adjusted saturation current |

|

| RSd | Geometry-adjusted source resistance |

|

| RDd | Geometry-adjusted drain resistance |

|

You can use these options to define transistor temperature, T:

Fixed temperature — The block uses a temperature that is independent of the circuit temperature when the Model temperature dependence using parameter in the Temperature settings of the SPICE NJFET block is set to

Fixed temperature. For this model, the block sets T equal to TFIXED.Device temperature — The block uses a temperature that depends on circuit temperature when the Model temperature dependence using parameter in the Temperature settings of the SPICE NJFET block is set to

Device temperature. For this model, the block defines temperature asWhere:

TC is the circuit temperature.

If there is not an Environment Parameters block in the circuit, TC is equal to 300.15 K.

If there is an Environment Parameters block in the circuit, TC is equal to the value that you specify for the Temperature parameter in the SPICE settings of the Environment Parameters block. The default value for the Temperature parameter is

300.15K.TOFFSET is the offset local circuit temperature.

Minimal conductance, GMIN, has a default value of

1e–12

1/Ohm. To specify a different value:

If there is not an Environment Parameters block in the transistor circuit, add one.

In the SPICE settings of the Environment Parameters block, specify the desired GMIN value for the GMIN parameter.

This table shows the equations that define the relationship between the gate-source current, Igs, and the gate-source voltage, Vgs. As applicable, the model parameters are first adjusted for temperature. For more information, see Temperature Dependence.

| Applicable Range of Vgs Values | Corresponding Igs Equation |

|---|---|

Where:

ISd is the geometry-adjusted saturation current.

Vt is the thermal voltage, such that .

ND is the emission coefficient.

q is the elementary charge on an electron.

k is the Boltzmann constant.

T is the transistor temperature. For more information, see Transistor Temperature

GMIN is the transistor minimum conductance. or more information, see Minimal Conduction

This table shows the relationship between the gate-drain current, Igd, and the gate-drain voltage, Vgd. As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vgd Values | Corresponding Igd Equation |

|---|---|

This table shows the relationship between the drain-source current, Ids, and the drain-source voltage, Vds, in normal mode (). As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vgs and Vgd Values | Corresponding Ids Equation |

|---|---|

Where:

Vto is the threshold voltage.

βd is the geometry-adjusted transconductance.

λ is the channel modulation.

This table shows the relationship between the drain-source current, Ids, and the drain-source voltage, Vds, in inverse mode (). As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vgs and Vgd Values | Corresponding Ids Equation |

|---|---|

This table shows the relationship between the gate-source charge, Qgs, and the gate-source voltage, Vgs. As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vgs Values | Corresponding Qgs Equation |

|---|---|

Where:

FC is the capacitance coefficient.

VJ is the junction potential.

CGSd is the zero-bias gate-source capacitance.

MG is the grading coefficient.

This table shows the relationship between the gate-drain charge, Qgd, and the gate-drain voltage, Vgd. As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vgd Values | Corresponding Qgd Equation |

|---|---|

Where CGDd is the geometry-adjusted zero-bias gate-drain capacitance.

The block provides this relationship between the saturation current IS and the transistor temperature T:

Where:

ISd is the geometry-adjusted saturation current.

Tmeas is the parameter extraction temperature.

XTI is the saturation current temperature exponent.

EG is the energy gap.

Vt is the thermal voltage, such that .

ND is the emission coefficient.

The relationship between the junction potential, VJ, and the transistor temperature T is

Where:

VJ is the junction potential.

The relationship between the gate-source junction capacitance, CGS, and the transistor temperature, T:

Where CGSd is the geometry-adjusted zero-bias gate-source capacitance.

The block uses the CGS(T) equation to calculate the gate-drain junction capacitance by substituting CGDd, the zero-bias gate-drain capacitance, for CGSd.

The relationship between the transconductance, β, and the transistor temperature T is

Where βd is the geometry-adjusted transconductance.

Assumptions and Limitations

The block does not support noise analysis.

The block applies initial conditions across junction capacitors and not across the block ports.

Ports

Conserving

Parameters

References

[1] G. Massobrio and P. Antognetti. Semiconductor Device Modeling with SPICE. 2nd Edition. New York: McGraw-Hill, 1993.

Extended Capabilities

Version History

Introduced in R2008a