HDL Verifier SystemVerilog DPI component generation with Synopsys VCS

This example was used in the video demonstration:

https://www.mathworks.com/videos/generate-systemverilog-dpi-components-for-simulation-with-synopsys-vcs-1495725854304.html

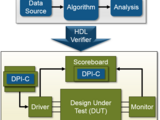

It illustrates how to re-use MATLAB functions and stimulus to more quickly build a Universal Verification Methodology testbench. Specifically it generates SystemVerilog DPI components from a MATLAB algorithm for use in a UVM scoreboard, and for a realistic video input for use as a UVM sequence item. The simulation is set up to run Synopsys VCS.

Citation pour cette source

MathWorks HDLVerifier Team (2024). HDL Verifier SystemVerilog DPI component generation with Synopsys VCS (https://www.mathworks.com/matlabcentral/fileexchange/63335-hdl-verifier-systemverilog-dpi-component-generation-with-synopsys-vcs), MATLAB Central File Exchange. Récupéré le .

Compatibilité avec les versions de MATLAB

Plateformes compatibles

Windows macOS LinuxCatégories

- FPGA, ASIC, and SoC Development >

- Code Generation > HDL Verifier > ASIC Testbench > DPI Generation for Simulink Subsystem >

- FPGA, ASIC, and SoC Development > HDL Verifier > ASIC Testbench > DPI Generation for Simulink Subsystem >

Tags

Community Treasure Hunt

Find the treasures in MATLAB Central and discover how the community can help you!

Start Hunting!Découvrir Live Editor

Créez des scripts avec du code, des résultats et du texte formaté dans un même document exécutable.

DPI_UVM_MATLAB_EnhancedEdgeDetect/

DPI_UVM_MATLAB_EnhancedEdgeDetect/DUT_HDL/

DPI_UVM_MATLAB_EnhancedEdgeDetect/codegen/dll/EED_scbd/html/resources/

DPI_UVM_MATLAB_EnhancedEdgeDetect/codegen/dll/Stimulus/html/resources/

| Version | Publié le | Notes de version | |

|---|---|---|---|

| 1.0.0.0 |