Les ingénieurs utilisent l'approche Model-Based Design avec MATLAB et Simulink pour concevoir des systèmes embarqués complexes et générer du code C, C++ et HDL de qualité production. En suivant le workflow de vérification de haute intégrité, les équipes peuvent utiliser les tests basés sur les simulations et l'analyse statique, pour apporter rigueur et automatisation à l'approche Model-Based Design, en vue de détecter les erreurs plus tôt et d'améliorer la qualité du système.

Définition des exigences

Le processus de développement commence avec les exigences informelles textuelles qui peuvent être répertoriées dans des documents, des feuilles de calcul ou des outils de gestion des exigences comme IBM Rational DOORS. Requirements Toolbox vous permet d'importer, de visualiser, de créer et de gérer les exigences en parallèle avec votre architecture, vos designs, votre code généré et vos artefacts de test. Vous pouvez créer un lien numérique, des exigences vers votre design, dans System Composer, Simulink, Stateflow, ou pour vos cas de test, dans Simulink Test. Grâce à cette traçabilité, vous pouvez identifier ce qui manque dans l'implémentation ou les tests, et comprendre rapidement l'impact d'une modification sur le design ou le banc d’essai.

Vous pouvez formaliser les exigences et les analyser pour en vérifier la cohérence, l'exhaustivité et la justesse afin de les valider plus tôt avec le bloc Requirements Table dans Requirements Toolbox. Les évaluations temporelles dans Simulink Test vous permettent de vérifier les exigences textuelles en spécifiant ces évaluations avec une sémantique précise en langage naturel qui peut être évaluée et débuggée.

Injection et analyse systématiques de défauts dans Simulink

Vous pouvez utiliser la simulation pour analyser les effets des pannes, des attaques et d’autres comportements anormaux afin de développer des exigences de sécurité et de sûreté, et de vérifier la robustesse du système. Simulink Fault Analyzer permet l'analyse systématique des effets des défauts, de la sécurité et de la sûreté, à l'aide de la simulation. Ce produit effectue des simulations d'injection de défauts sans modifier votre design. Vous pouvez gérer les défauts et les attaques modélisés dans Simulink, Simscape et System Composer. Simulation Data Inspector vous permet d'analyser les effets des défauts et des attaques. Vous pouvez effectuer des analyses de sensibilité à l’aide du panneau Simulations multiples. Vous pouvez effectuer des analyses de sécurité, comme l'analyse des modes de défaillance et de leurs effets (AMDEC (5:50)) et l'analyse de cybersécurité (par exemple, TARA) tout en exploitant la simulation. Simulink Fault Analyzer vous permet de créer des connexions formelles entre les défauts, les attaques, les dangers, la logique de détection et d'atténuation des défauts et d'autres artefacts (avec Requirements Toolbox).

Conformité aux normes de certification

Automatisez la vérification de conformité des modèles et du code vis-à-vis des normes comme DO-178, ISO 26262, IEC 61508 et IEC 62304, et des directives du MathWorks Advisory Board (MAB). Simulink Check propose des règles de vérification et des métriques reconnues dans l'industrie permettant d'identifier les violations des normes et des directives lors du développement. Vous pouvez créer des règles de vérification personnalisées afin d'assurer la conformité à vos propres normes ou directives internes. L'IEC Certification Kit (for ISO 26262 and IEC 61508) et le DO Qualification Kit (for DO-178 and DO-254) offrent des artefacts de qualification d'outils, des certificats et des suites de tests pour vous aider à qualifier les produits de génération de code et de vérification, ainsi que pour rationaliser la certification de vos systèmes embarqués.

Preuve d’absence d'erreurs et vérification formelle des exigences

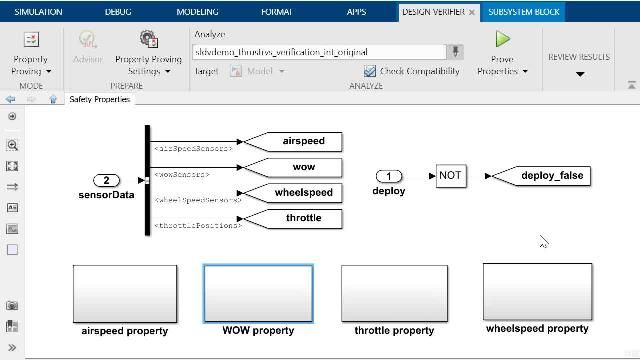

La vérification formelle permet d'identifier des erreurs de design cachées qui entraînent par exemple des dépassements d'entiers, de la logique morte, des violations d'accès aux tableaux et des divisions par zéro, tout ceci sans simuler le design. Simulink Design Verifier peut vérifier formellement que votre design ne présente aucune erreur ou vulnérabilité de sécurité. Cet outil peut également prouver que votre design est conforme aux exigences critiques. S'il détecte une exception, il génère un contre-exemple pour le débuggage.

Analyse de la couverture de test du modèle

Il est essentiel d'identifier ce qui n’est pas couvert par les tests, les fonctionnalités indésirables ou les erreurs relatives aux exigences. Simulink Coverage calcule la proportion du modèle ou du code généré éprouvée pendant les tests. Il applique des métriques reconnues dans l'industrie, notamment les conditions, les décisions, les conditions/décisions modifiées (MC/DC) et les objectifs de couverture personnalisés. Simulink Design Verifier peut générer automatiquement des cas de test afin d'analyser les problèmes liés à une couverture incomplète et vous permettre d'atteindre vos objectifs de couverture structurelle et fonctionnelle pour les tests comparatifs.

Analyse statique de code

Pour vérifier du code écrit manuellement ou généré automatiquement, les produits Polyspace utilisent des méthodes formelles afin de trouver les bugs et prouver l'absence d'erreurs run-time critiques sans exécuter de code ni de cas de test. Polyspace Bug Finder vérifie et documente la conformité aux normes telles que MISRA, ISO 26262, IEC 61508, DO-178 et aux réglementations FDA. Vous pouvez vérifier les vulnérabilités de sécurité logicielle et la conformité aux normes telles que CWE, CERT-C, ISO/IEC 17961 et bien d'autres. Polyspace Code Prover effectue une analyse statique permettant de prouver l'absence d'overflow, de division par zéro, d’accès hors limites à des tableaux et d’autres erreurs d’exécution dans le code source C et C++.