La traduction de cette page n'est pas à jour. Cliquez ici pour voir la dernière version en anglais.

Génération de code HDL

Pour implémenter un design DSP sur des FPGA ou des ASIC, utilisez HDL Coder™ pour générer du code à partir de Simulink ou MATLAB. L’outil permet de générer du code VHDL® et Verilog® synthétisable et portable mais aussi des test benches VHDL et Verilog pour simuler, tester et vérifier rapidement le code généré.

Les blocs supportés dans DSP System Toolbox™ et DSP HDL Toolbox comprennent des filtres, des opérations mathématiques et sur les signaux, ainsi que d’autres algorithmes optimisés en termes d’utilisation des ressources et de la performance, par exemple les blocs FFT (DSP HDL Toolbox), Discrete FIR Filter (DSP HDL Toolbox) et NCO (DSP HDL Toolbox). DSP HDL Toolbox™ propose des blocs et des System objects qui implémentent des architectures compatibles hardware. Les blocs et System objects de DSP HDL Toolbox comprennent également des interfaces streaming haut débit atteignant plusieurs giga-échantillons par seconde (GSPS), autrement dit des fréquences de super-échantillonnage. Ils proposent aussi des signaux de contrôle hardware ainsi que des options permettant de sélectionner différentes implémentations hardware de leurs algorithmes.

Pour un exemple montrant comment générer du code HDL à partir d’un bloc DSP System Toolbox avec HDL Coder, veuillez consulter Multichannel FIR Filter for FPGA. Pour une présentation de DSP HDL Toolbox, veuillez consulter Implement FFT Algorithm for FPGA (DSP HDL Toolbox).

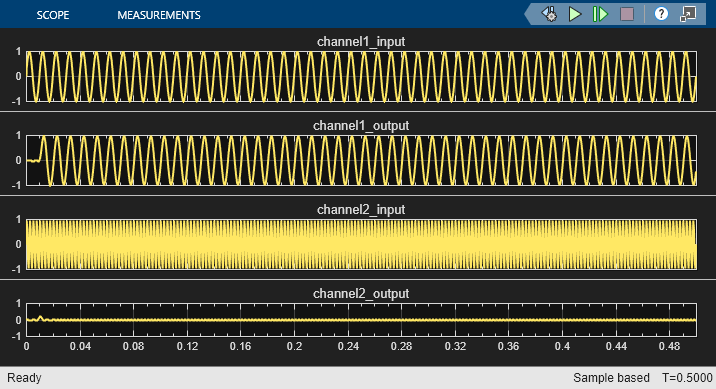

Pour débugger vos designs dans Simulink ou MATLAB, utilisez l’affichage de formes d’onde dans Logic Analyzer.

Outil de visualisation Simulink

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |

Rubriques

- Find Blocks That Support HDL Code Generation

Filter for blocks that support HDL code generation in the Simulink library browser and in documentation.

- High-Throughput HDL Algorithms (DSP HDL Toolbox)

Choose a block that supports frame-based processing for HDL code generation.

- HDL Filter Architectures

HDL code generation parameters to control speed and area tradeoffs in filter architectures.

- Subsystem Optimizations for Filters

Select resource sharing and pipeline optimization options.

- Visualize Multiple Signals Using Logic Analyzer

Visualize multiple signals of a programmable FIR filter by using the Logic Analyzer app.