Supported Data Types

Converting HDL Data to Send to MATLAB or Simulink

If your HDL application needs to send HDL data to a MATLAB® function or a Simulink® block, you may first need to convert the data to a type supported by MATLAB and the HDL Verifier™ software.

To program a MATLAB function or a Simulink block for an HDL model, you must understand the type conversions required by your application. You may also need to handle differences between the array indexing conventions used by the HDL you are using and MATLAB (see following section).

The data types of arguments passed in to the function determine the following:

The types of conversions required before data is manipulated

The types of conversions required to return data to the HDL simulator

The following table summarizes how the HDL Verifier software converts supported VHDL® data types to MATLAB types based on whether the type is scalar or array.

VHDL to MATLAB Data Type Conversions

| VHDL Types... | As Scalar Converts to... | As Array Converts to... |

|---|---|---|

STD_LOGIC, STD_ULOGIC,

and BIT | A character that matches the character literal for the desired logic state. | |

STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, BIT_VECTOR, SIGNED,

and UNSIGNED | A column vector of characters (as defined in VHDL Conversions for the HDL Simulator) with one bit per character. | |

Arrays of STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, BIT_VECTOR, SIGNED,

and UNSIGNED | An array of characters (as defined above) with a size that is equivalent to the VHDL port size. | |

INTEGER and NATURAL | Type int32. | Arrays of type Note

|

REAL | Type double. | Arrays of type Note

|

TIME | Type double for time values in seconds and

type int64 for values representing simulator time

increments (see the description of the 'time' option

in hdldaemon). | Arrays of type double or int64 with

a size that is equivalent to the VHDL port size. |

| Enumerated types | Character vector or string scalar that contains the MATLAB representation of a VHDL label or character literal. For example, the label

high converts to 'high'

and the character literal 'c' converts to

'''c'''. | Cell array of character vectors or string array with each element equal to a label for the

defined enumerated type. Each element is the MATLAB representation of a VHDL label or character literal. For example, the vector

(one, '2', three) converts to the column

vector ['one'; '''2'''; 'three']. A user-defined

enumerated type that contains only character literals, and then

converts to a vector or array of characters as indicated for the

types STD_LOGIC_VECTOR,

STD_ULOGIC_VECTOR,

BIT_VECTOR, SIGNED, and

UNSIGNED. |

The following table summarizes how the HDL Verifier software converts supported Verilog® data types to MATLAB types. The software supports packed arrays up to 128bits for Verilog.

Verilog-to-MATLAB Data Type Conversions

| Verilog Types... | Converts to... |

|---|---|

wire, reg | A character or a column vector of characters that matches the character literal for the desired logic states (bits). |

The following table summarizes how the HDL Verifier software converts supported SystemVerilog data types to MATLAB types. The software supports packed arrays up to 128bits for SystemVerilog.

SystemVerilog-to-MATLAB Data Type Conversions

| SystemVerilog Types... | Converts to... |

|---|---|

wire, reg,

logic | A character or a column vector of characters that matches the character literal for the desired logic states (bits). |

integer

| A 32-element column vector of characters that matches the character literal for the desired logic states (bits). Supported for outputs only. |

bit | boolean/ufix1 |

byte | int8/uint8 |

shortint | int16/uint16 |

int | int32 |

longint | int64/uint64 |

real | double |

packed array (bit/logic vector) |

|

SystemVerilog-to-Simulink Data Type Conversions

| SystemVerilog Types... | Converts to... |

|---|---|

wire, reg,

logic | A character or a column vector of characters that matches the character literal for the desired logic states (bits). |

integer

| A 32-element column vector of characters that matches the character literal for the desired logic states (bits). Supported for outputs only. |

bit | boolean/ufix1 |

byte | int8/uint8 |

shortint | int16/uint16 |

int | int32 |

longint | int64/uint64 |

real | double |

packed array (bit/logic vector) |

|

unpacked array | Simulink vector. For more details see Simulink Support for SystemVerilog Unpacked Arrays. |

struct | Each struct member is represented as a singular port. Note

|

Note

SystemVerilog support includes signals of the above types. The following SystemVerilog types are not supported:

shortrealSystemVerilog typeunionSystemVerilog typeNested structures

SystemVerilog interfaces

Bit-Vector Indexing Differences Between MATLAB and HDL

In HDL, you have the flexibility to define a bit-vector with either MSB-0 or LSB-0 numbering. In MATLAB, bit-vectors are always considered LSB-0 numbering. In order to prevent data corruption, it is recommended that you use LSB-0 indexing for your HDL interfaces.

If you define a logic vector in VHDL as:

signal s1 : std_logic_vector(7 downto 0);

Or in Verilog as:

reg[7:0] s1;

It is mapped to int8 in MATLAB, with s1[7] as the MSB. Alternatively, if you define your VHDL logic vector as:

signal s1 : std_logic_vector(0 to 7);

Or in Verilog as:

reg[0:7] s1;

It is mapped to int8 in MATLAB, with s1[0] as the MSB.

Array Indexing Differences Between MATLAB and HDL

In multidimensional arrays, the same underlying OS memory buffer

maps to different elements in MATLAB and the HDL simulator (this

mapping only reflects different ways the different languages offer

for naming the elements of the same array). When you use both the matlabtb and matlabcp functions,

be careful to assign and interpret values consistently in both applications.

In HDL, a multidimensional array declared as:

type matrix_2x3x4 is array (0 to 1, 4 downto 2) of std_logic_vector(8 downto 5);

has a memory layout as follows:

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 dim2 4 4 4 4 3 3 3 3 2 2 2 2 4 4 4 4 3 3 3 3 2 2 2 2 dim3 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5 8 7 6 5

This same layout corresponds to the following MATLAB 4x3x2 matrix:

bit 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 - dim1 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 dim2 1 1 1 1 2 2 2 2 3 3 3 3 1 1 1 1 2 2 2 2 3 3 3 3 dim3 1 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2

Therefore, if H is the HDL array and M is the MATLAB matrix, the following indexed values are the same:

b1 H(0,4,8) = M(1,1,1) b2 H(0,4,7) = M(2,1,1) b3 H(0,4,6) = M(3,1,1) b4 H(0,4,5) = M(4,1,1) b5 H(0,3,8) = M(1,2,1) b6 H(0,3,7) = M(2,2,1) ... b19 H(1,3,6) = M(3,2,2) b20 H(1,3,5) = M(4,2,2) b21 H(1,2,8) = M(1,3,2) b22 H(1,2,7) = M(2,3,2) b23 H(1,2,6) = M(3,3,2) b24 H(1,2,5) = M(4,3,2)

You can extend this indexing to N-dimensions. In general, the dimensions—if numbered from left to right—are reversed. The right-most dimension in HDL corresponds to the left-most dimension in MATLAB.

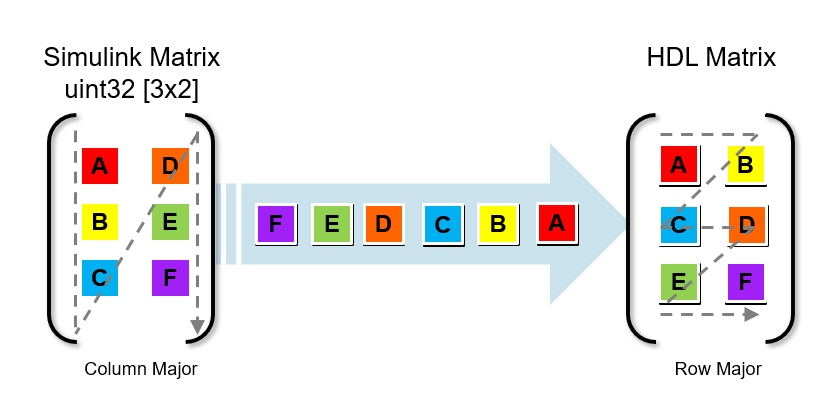

Array Indexing - Column Major

When you perform a Simulink cosimulation with a SystemVerilog DUT, and the DUT includes an

unpacked array port, note that HDL Verifier indexes the array in a column major order. For example, for a 3x2 HDL

matrix defined as:

logic [31:0] In1 [0:2][0:1]

In this figure, indexing the Simulink matrix in column-major would read the elements column by column, in this order:

A, B, C, D, E, F

m1 is the Simulink matrix and m2 is the HDL matrix, the following

indexed values are the same (assuming the Simulink index mode is

0-base):m1(0,0) = m2(0,0) = A m1(1,0) = m2(0,1) = B m1(2,0) = m2(1,0) = C m1(0,1) = m2(1,1) = D m1(1,1) = m2(2,0) = E m1(2,1) = m2(2,1) = F

Converting Data for Manipulation

Depending on how your simulation MATLAB function uses the data it receives from the HDL simulator, you may need to code the function to convert data to a different type before manipulating it. The following table lists circumstances under which you would require such conversions.

Required Data Conversions

| If You Need the Function to... | Then... |

|---|---|

Compute numeric data that is received as a type other than double |

Use the datas(inc+1) = double(idata); |

| Convert a standard logic or bit vector to an unsigned integer or positive decimal |

Use the uval = mvl2dec(oport.val) This example assumes the standard logic or bit vector is

composed of the character literals The See |

| Convert a standard logic or bit vector to a negative decimal |

Use the following application of the

suval = mvl2dec(oport.val, true); This example assumes the standard logic or bit vector is

composed of the character literals |

Examples

The following code excerpt illustrates data type conversion of data passed in to a callback:

InDelayLine(1) = InputScale * mvl2dec(iport.osc_in',true);

This example tests port values of VHDL type STD_LOGIC and STD_LOGIC_VECTOR by

using the all function as follows:

all(oport.val == '1' | oport.val == '0')

This example returns True if all elements

are '1' or '0'.

Converting Data for Return to the HDL Simulator

If your simulation MATLAB function needs to return data to the HDL simulator, you may first need to convert the data to a type supported by the HDL Verifier software. The following tables list circumstances under which such conversions are required for VHDL and Verilog.

Note

When data values are returned to the HDL simulator, the char array size must match the HDL type, including leading zeroes, if applicable. For example:

oport.signal = dec2mvl(2)

will only work if signal is a 2-bit type

in HDL. If the HDL type is anything else, you must specify

the second argument:

oport.signal = dec2mvl(2, N)

where N is the number of bits in the HDL data type.

VHDL Conversions for the HDL Simulator

| To Return Data to an IN Port of Type... | Then... |

|---|---|

STD_LOGIC, STD_ULOGIC,

or BIT |

Declare the data as a character that matches the character

literal for the desired logic state. For

iport.s1 = 'X'; %STD_LOGIC iport.bit = '1'; %BIT |

STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, BIT_VECTOR, SIGNED,

or UNSIGNED |

Declare the data as a column vector or row vector of characters (as defined above) with one bit per character. For example: iport.s1v = 'X10ZZ'; %STD_LOGIC_VECTOR iport.bitv = '10100'; %BIT_VECTOR iport.uns = dec2mvl(10,8); %UNSIGNED, 8 bits |

Array of STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, BIT_VECTOR, SIGNED,

or UNSIGNED | Declare the data as an array of type character with a size that is equivalent to the VHDL port size. See Array Indexing Differences Between MATLAB and HDL. |

INTEGER or NATURAL | Declare the data as an array of type iport.int = int32(1:10)'; Note

|

REAL | Declare the data as an array of type iport.dbl = ones(2,2); Note

|

TIME | Declare a VHDL

iport.t1 = int64(1:10)'; %Simulator time

%increments

iport.t2 = 1e-9; %1 nsec

|

| Enumerated types | Declare the data as a character vector or string scalar for scalar ports or a cell

array of character vectors or string array for array ports with

each element equal to a label for the defined enumerated type.

The iport.char = {'''A''', '''B'''}; %Character

%literal

iport.udef = 'mylabel'; %User-defined label

|

| Character array for standard logic or bit representation |

Use the oport.slva =dec2mvl([23 99],8)'; |

Verilog Conversions for the HDL Simulator

To Return Data to an input Port

of Type... | Then... |

|---|---|

reg, wire |

Declare the data as a character or a column vector of characters that matches the character literal for the desired logic state. For example: iport.bit = '1'; |

SystemVerilog Conversions for the HDL Simulator

To Return Data to an input Port

of Type... | Then... |

|---|---|

reg, wire,

logic |

Declare the data as a character or a column vector of characters that matches the character literal for the desired logic state. For example: iport.bit = '1'; |

integer | Declare the data as a 32-element column vector of characters (as defined above) with one bit per character. |

Packed arrays are supported up to 128bits.

Note

SystemVerilog support includes only scalar signals of the above types. The following SystemVerilog types are not supported:

Arrays and multi-dimensional arrays

shortrealSystemVerilog typeSystemVerilog aggregate types such as

unionandstructSystemVerilog interfaces

Simulink Handling of Wide HDL Ports

When your HDL module has a port that is wider than 128 bits, Simulink creates a vector of ports to represent this port. The Cosimulation Wizard infers the size of the HDL port. You can then set the Simulink Word Length parameter in the HDL Cosimulation block.

For input ports — Simulink port dimensions are determined at compile time by the data type of the driving signal. For example:

When HDL Word Length = 150 and Simulink Word Length = 50, HDL Verifier allows a Simulink port with data width of 50 bits, and dimensions of size 3 such as

sfix50(3)orufix50(3).When HDL Word Length = 140 and Simulink Word Length = 50, HDL Verifier packs 150 bits of Simulink into 140 bits of HDL. HDL Verifier ignores the 10 most significant bits (MSB) of the last word.

For output ports

HDL Verifier creates a vector of ports to represent the output port. For example:

When HDL Word Length = 150 and Simulink Word Length = 50, HDL Verifier creates a Simulink port with data width of 50 bit. For example

sfix50(3)orufix50(3).When HDL Word Length = 150 and Simulink Word Length = 60, HDL Verifier creates a Simulink port with data width of 60, such as

sfix60(3)orufix60(3). Since the HDL word has only 150 bits, and the Simulink port requires 180 bits, 30 bits are padded or sign extended.When HDL Word Length = 140 and Simulink Word Length = 50, every 50 bits of the HDL output are represented as a Simulink word. The 10 MSB of the last Simulink word are unused and extended according to the Sign parameter.

Simulink Support for SystemVerilog Unpacked Arrays

When you have an existing HDL DUT — When you use the Cosimulation Wizard to import a SystemVerilog DUT that includes unpacked arrays on the interface, HDL Verifier follows this convention:

For input ports, the HDL Cosimulation block can accept matrix data from Simulink.

For output ports, the HDL Cosimulation block outputs a flat vector of data.

HDL Verifier interprets arrays and matrices in column major ordering. For more information, see Array Indexing - Column Major.

For example, if your SystemVerilog DUT defines this interface, with a 2-by-5 unpacked array input and output port:

module myDUT

(input logic clk,

input logic clk_en,

input logic[31:0] In1[0:1] [0:4],

output logic[31:0] Out1[0:1] [0:4],

output logic ce_out);You can now write a Simulink testbench that drives an input with ten elements of

int32, such as int32 [2x5]. The output

port maps to a flat array of ten elements: int32 [10x1].

![HDL Cosimulation block showing input port with data type int32[2x5] and output port of type int32(10)](unpackedarray0.png)

When you generate an HDL DUT — When you use the Workflow Advisor (HDL Coder) to generate a SystemVerilog DUT, HDL Verifier can generate a cosimulation testbench model for only one-dimensional arrays (vectors) on the DUT interface.

Vivado Support for Unpacked Arrays

Since the Vivado simulator cannot differentiate between packed and unpacked dimensions, HDL Verifier treats the lowest dimension as a packed dimension and the rest as unpacked dimensions.

For example:

If the SystemVerilog has a port defined as

Logic [7:0][3:0] dataA, Simulink maps it to an array of eight elements with data-typefixdt4.If the SystemVerilog has a port defined as

Logic [3:0][7:0] dataB [1:3][4:6], Simulink maps it to an array of 36 elements (the product of3*3*4), with data-typefixdt8.

Simulink Support for Verilog and SystemVerilog Enumerations

When you have an existing HDL DUT — When you use

the Cosimulation Wizard to import a DUT that

includes a port of type enum on the interface, HDL Verifier maps the port to a fixed-point logic vector. The size of that logic

vector is determined by the number of bits required to represent the

enum type.

For example, if your SystemVerilog DUT defines this interface, with a BasicColors

input and output port, the ports map to an input or output of type

ufix2.

typedef enum logic [1:0] {

Red,

Yellow,

Blue

} t_BaiscColors;

module scalarEnums

( input t_BasicColors In1,

output t_BasicColors Out1);

When you generate an HDL DUT — When you use the

Workflow

Advisor (HDL Coder) to generate a Verilog or SystemVerilog DUT, HDL Verifier generates a cosimulation testbench model and converts the types to use

the Simulink.IntEnumType data type that match the DUT. For more

about Simulink enumerations, see Code Generation for Enumerations (Simulink).

VHDL does not support enumerated types.

See Also

Cosimulation Wizard | HDL Cosimulation | hdlverifier.HDLCosimulation