La traduction de cette page n'est pas à jour. Cliquez ici pour voir la dernière version en anglais.

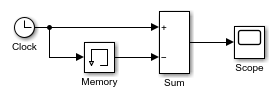

Memory

Générer l’entrée à partir du pas de temps précédent

Bibliothèques :

Simulink /

Discrete

HDL Coder /

Discrete

Description

Le bloc Memory bloque son entrée et la retarde d’un pas de temps d’intégration majeur. Lorsqu’il est placé dans un sous-système itérateur, il bloque son entrée et la retarde d’une itération. Ce bloc accepte les signaux continus et discrets. Le bloc accepte une seule entrée et génère une seule sortie. Chaque signal peut être un scalaire, un vecteur, une matrice ou un tableau nD. Si l’entrée n’est pas un scalaire, le bloc bloque tous les éléments de l’entrée et les retarde du même pas de temps.

Spécifiez la sortie du bloc pour le premier pas de temps avec le paramètre Initial condition. Sélectionnez ce paramètre avec soin pour réduire le risque de comportement indésirable en sortie. Cependant, vous ne pouvez pas spécifier le pas d’échantillonnage. Le pas d’échantillonnage de ce bloc dépend du type de solveur utilisé, mais vous pouvez également choisir de l’hériter. Le paramètre Inherit sample time détermine si le pas d’échantillonnage est hérité ou s’il est basé sur le solveur.

Conseil

Évitez d’utiliser le bloc Memory lorsque les deux conditions suivantes sont remplies :

Votre modèle utilise le solveur à pas variable

ode15souode113.L’entrée vers le bloc change pendant la simulation.

Lorsque le bloc Memory hérite d’un pas d’échantillonnage discret, le bloc est analogue au bloc Unit Delay. Cependant, le bloc Memory ne supporte pas l’enregistrement des états. Si l’enregistrement de l’état final est nécessaire, utilisez un bloc Unit Delay à la place.

Comparaison avec des blocs similaires

Les blocs Memory, Unit Delay et Zero-Order Hold ont un fonctionnement similaire mais offrent des possibilités différentes. De plus, l’objectif de chaque bloc est différent.

Le tableau suivant indique l’utilisation recommandée pour chaque bloc.

| Bloc | Objectif du bloc | Exemples de référence |

|---|---|---|

| Unit Delay | Implémenter un délai avec un pas d’échantillonnage discret spécifié. Le bloc accepte et génère des signaux ayant un pas d’échantillonnage discret. |

|

| Memory | Implémenter un délai d’un pas de temps d’intégration majeur. Dans l’idéal, le bloc accepte des signaux continus (ou fixes dans un pas de temps mineur) et génère un signal de sortie fixe dans un pas de temps mineur. |

|

| Zero-Order Hold | Convertir un signal d’entrée avec un pas d’échantillonnage continu en un signal de sortie avec un pas d’échantillonnage discret. |

Chaque bloc offre les fonctionnalités suivantes.

| Fonctionnalité | Memory | Unit Delay | Zero-Order Hold |

|---|---|---|---|

| Spécification de la condition initiale | Oui | Oui | Non car la sortie du bloc au temps t = 0 doit être identique à la valeur en entrée. |

| Spécification du pas d’échantillonnage | Non car le bloc peut uniquement hériter du pas d’échantillonnage du bloc d’origine ou du solveur utilisé pour le modèle entier. | Oui | Oui |

| Support des signaux basés sur des trames | Non | Oui | Oui |

| Support de l’enregistrement des états | Non | Oui | Non |

Support des bus

Le bloc Memory est compatible avec les bus. L’entrée peut être un signal de bus virtuel ou non virtuel soumis aux restrictions suivantes :

Initial condition doit être nulle, un scalaire non nul ou une structure numérique finie.

L’entrée ne peut pas être un bus virtuel si Initial condition est nulle ou une structure et que vous spécifiez un State name.

Vous ne pouvez pas spécifier de State name si Initial condition est un scalaire non nul.

Pour plus d’informations sur la spécification d’une structure de condition initiale, consultez Specify Initial Conditions for Bus Elements.

Tous les signaux d’un bus non virtuel utilisé comme entrée d’un bloc Memory doivent avoir le même pas d’échantillonnage, même si les éléments de l’objet de bus associé spécifient des pas d’échantillonnage hérités. Vous pouvez utiliser un bloc Rate Transition pour modifier le pas d’échantillonnage d’un seul signal ou de tous les signaux d’un bus. Pour plus d’informations, consultez Modify Sample Times for Nonvirtual Buses et Blocs compatibles avec les bus.

Vous pouvez utiliser un tableau de bus comme signal d’entrée d’un bloc Memory. Vous pouvez spécifier le paramètre Initial condition avec :

La valeur

0. Dans ce cas, tous les signaux individuels dans le tableau de bus utilisent la valeur initiale0.Un tableau de structures qui spécifie une condition initiale pour chacun des signaux individuels dans le tableau de bus.

Une structure scalaire qui spécifie une condition initiale pour chacun des éléments définis par le type de bus. Utilisez cette technique pour spécifier les mêmes conditions initiales pour chaque bus dans le tableau.

Pour en savoir plus sur la définition et l’utilisation d’un tableau de bus, consultez Group Nonvirtual Buses in Arrays of Buses.

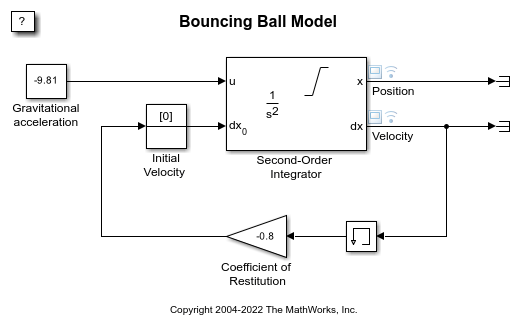

Exemples

Exemples étendus

Ports

Entrée(s)

Sortie(s)

Paramètres

Caractéristiques des blocs

Types de données |

|

Traversée directe |

|

Signaux multidimensionnels |

|

Signaux de taille variable |

|

Détection des passages à zéro |

|

a Les caractéristiques de traversée (feedthrough) directe de ce bloc dépendent des valeurs des paramètres du bloc. | |

Capacités étendues

Historique des versions

Introduit avant R2006a