Les experts du domaine et les ingénieurs hardware utilisent MATLAB et Simulink pour développer des applications prototypes et de production en vue d'un déploiement sur cartes SoC et FPGA Microchip®.

Avec MATLAB et Simulink, vous pouvez :

- Modéliser une architecture hardware au niveau système

- Programmer votre FPGA sans écrire de code

- Simuler et débugger votre FPGA à l'aide des outils MATLAB et Simulink

- Réaliser des designs FPGA et SoC de production

« En tant qu'ingénieur en systèmes mécatroniques, mon domaine d'expertise relève des systèmes de contrôle et de leurs modèles, mais pas du code HDL et des cartes FPGA. Avec l'approche Model-Based Design, je peux utiliser mes connaissances approfondies du contrôleur et du système contrôlé pour m'occuper davantage des tâches normalement gérées par des ingénieurs FPGA, et ainsi réduire leur charge de travail.

Rob Reilink, DEMCON

Utiliser MATLAB avec des SoC et FGPA de Microchip

La modélisation pour la programmation FPGA

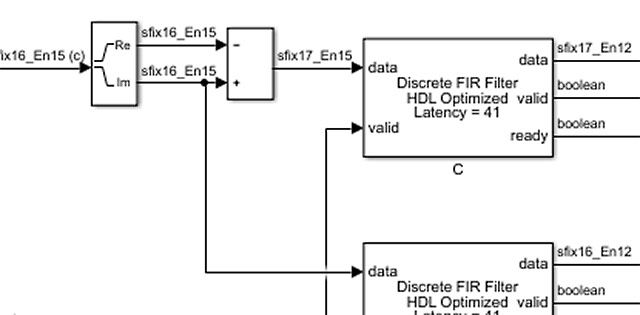

Ajoutez une architecture hardware à votre algorithme en utilisant MATLAB et Simulink. Cela comprend la quantification en virgule fixe, qui vous permet d'utiliser des ressources de manière plus efficace, et la génération de code en virgule flottante native, grâce à laquelle vous pouvez programmer des FPGA plus facilement. Réutilisez vos tests et votre algorithme de référence pour simuler chaque amélioration successive.

HDL Coder génère du code VHDL ou Verilog synthétisable directement depuis les blocs Simulink et les fonctions MATLAB compatibles HDL pour des applications telles que le traitement du signal, les télécommunications, le contrôle de moteur et d'électronique de puissance et le traitement d'images/de vidéos.

En savoir plus

- DEMCON réduit le temps de développement de ses instruments chirurgicaux contrôlés par FPGA

- Adopter l'approche Model-Based Design pour le développement de FPGA, ASIC et SoC (15:25)

- La virgule fixe simplifiée pour la programmation FPGA (30:45)

- Générer du code HDL en virgule flottante pour du hardware FPGA et ASIC (9:19)

Découvrir les produits

Programmation de SoC et FGPA de Microchip

HDL Coder vous guide tout au long des étapes de programmation de votre FPGA ou SoC directement depuis Simulink, sans que vous ayez besoin d'écrire du code. Avec HDL Coder, vous pouvez optimiser et générer du code VHDL® ou Verilog® synthétisable, ainsi que des interfaces AXI à intégrer dans un SoC. Puis, il est possible d'utiliser Embedded Coder pour générer du code C/C++ afin de programmer le software s'exécutant sur le processeur embarqué.

À l'aide de HDL Coder, vous pouvez spécifier votre FGPA Microchip comme dispositif cible. Vous pouvez créer automatiquement un projet dans Libero® SoC Design Suite, effectuer une synthèse et exécuter un processus de placement-routage .

En savoir plus

Découvrir les produits

Simulation et débuggage de FPGA

HDL Verifier réutilise vos environnements de test MATLAB et Simulink pour vérifier votre design FPGA.

Avec la cosimulation, vous pouvez lancer automatiquement votre test bench MATLAB ou Simulink connecté à votre design Verilog ou VHDL, lui-même exécuté sur un simulateur de Mentor Graphics ou Cadence Design Systems.

La simulation FPGA-in-the-loop connecte votre test bench MATLAB ou Simulink à des cartes FPGA Microchip compatibles via Ethernet.

Tester votre design implémenté dans votre test bench MATLAB ou Simulink.

Design de FPGA et SoC de production

Les experts du domaine et les ingénieurs hardware utilisent MATLAB et Simulink pour collaborer sur le design FPGA et SoC de production pour des applications de télécommunications, de traitement de vidéos/d'images, de contrôle de moteur/d'électronique de puissance et des applications critiques.

Les optimisations de synthèse de haut niveau de HDL Coder vous aident à atteindre vos objectifs de design tout en conservant une traçabilité entre le code RTL généré, le modèle et les exigences. Ce dernier point est d'autant plus important pour les workflows de développement de systèmes critiques comme le DO-254. En plus du code VHDL et Verilog synthétisable, HDL Coder génère des cœurs IP qui s'intègrent à Libero pour l'intégration système. HDL Verifier génère des modèles de vérification qui contribuent à l'accélération du développement de test benches.

En savoir plus

- Pipelining distribué : optimisation de la vitesse

- Partage des ressources pour l'optimisation de surface

- Commande vectorielle d'une machine synchrone à aimants permanents (PMSM)

- Améliorer la vérification RTL en se connectant à MATLAB (41:03)

- Utiliser l'approche Model-Based Design pour assurer la conformité à la certification DO-254

Découvrir les produits